- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299200 > 7140LA25JGI (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 8 DUAL-PORT SRAM, 25 ns, PQCC52 PDF資料下載

參數(shù)資料

| 型號(hào): | 7140LA25JGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 1K X 8 DUAL-PORT SRAM, 25 ns, PQCC52 |

| 封裝: | 0.750 X 0.750 INCH, 0.170 INCH HEIGHT, GREEN, PLASTIC, LCC-52 |

| 文件頁數(shù): | 8/19頁 |

| 文件大?。?/td> | 149K |

| 代理商: | 7140LA25JGI |

IDT7130SA/LA and IDT7140SA/LA

High-Speed 1K x 8 Dual-Port Static SRAM

Military, Industrial and Commercial Temperature Ranges

16

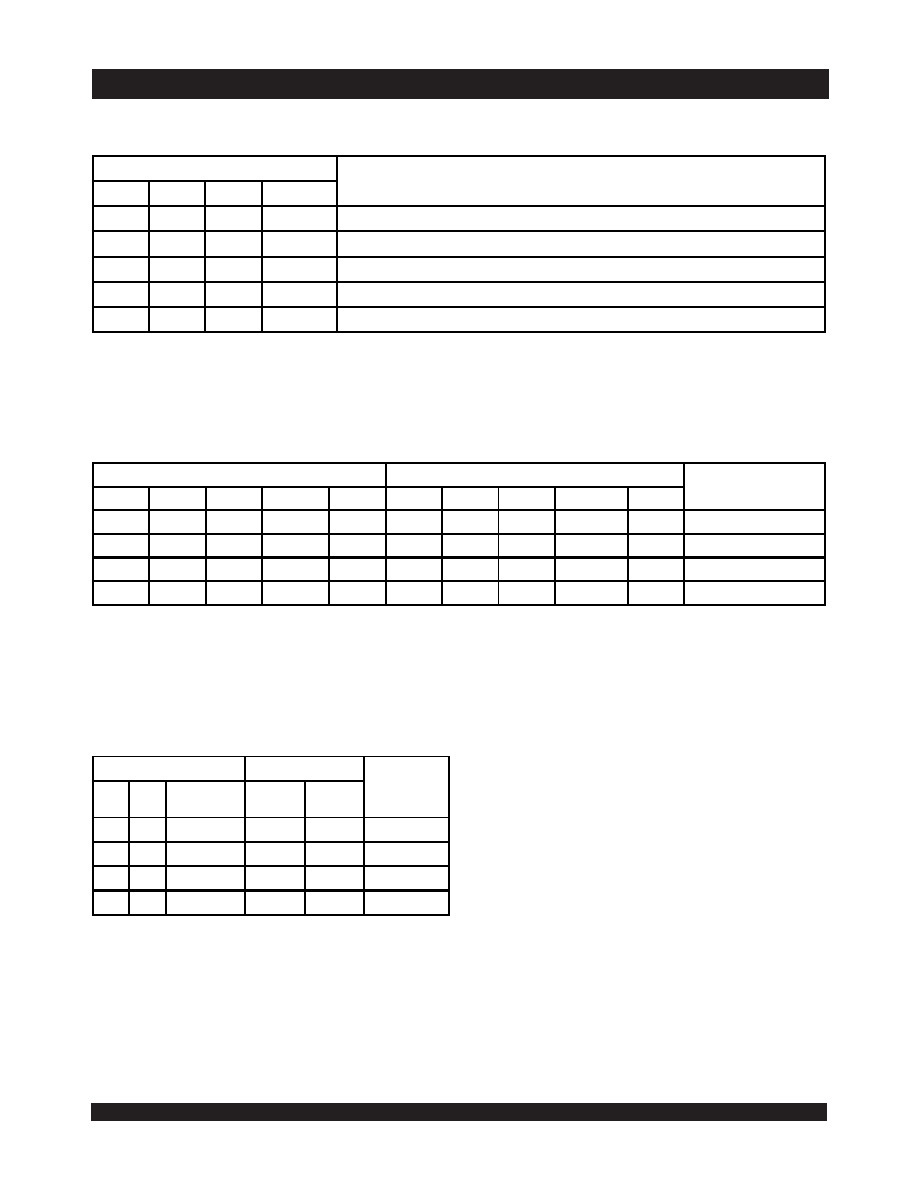

Truth Table I — Non-Contention Read/Write Control(4)

Truth Tables

Truth Table II — Interrupt Flag(1,4)

Truth Table III — Address BUSY

Arbitration

NOTES:

1. Pins

BUSYL and BUSYR are both outputs for IDT7130 (master). Both are inputs for

IDT7140 (slave).

BUSYX outputs on the IDT7130 are open drain, not push-pull

outputs. On slaves the

BUSYX input internally inhibits writes.

2. 'L' if the inputs to the opposite port were stable prior to the address and enable inputs

of this port. 'H' if the inputs to the opposite port became stable after the address and

enable inputs of this port. If tAPS is not met, either

BUSYL or BUSYR = LOW will

result.

BUSYL and BUSYR outputs can not be LOW simultaneously.

3. Writes to the left port are internally ignored when

BUSYL outputs are driving LOW

regardless of actual logic level on the pin. Writes to the right port are internally

ignored when

BUSYR outputs are driving LOW regardless of actual logic level on

the pin.

NOTES:

1. A0L – A10L A0R – A10R.

2. If

BUSY = L, data is not written.

3. If

BUSY = L, data may not be valid, see tWDD and tDDD timing.

4. 'H' = VIH, 'L' = VIL, 'X' = DON’T CARE, 'Z' = HIGH IMPEDANCE

NOTES:

1. Assumes

BUSYL = BUSYR = VIH

2. If

BUSYL = VIL, then No Change.

3. If

BUSYR = VIL, then No Change.

4. 'H' = HIGH,' L' = LOW,' X' = DON’T CARE

Inputs(1)

Function

R/

W

CE

OE

D0-7

X

H

X

Z

Port Disabled and in Power-Down Mode, ISB2 or ISB4

XH

X

Z

CER = CEL = VIH, Power-Down Mode, ISB1 or ISB3

LL

X

DATAIN

Data on Port Written into Memory(2)

HL

L

DATAOUT

Data in Memory Output on Port

(3)

H

L

H

Z

High Impedance Outputs

2689 tbl 13

Left Port

Right Port

Function

R/

WL

CEL

OEL

A9L-A0L

INTL

R/

WR

CER

OER

A9R-A0R

INTR

L

X3FF

XXXX

X

L(2)

Set Right

INTR Flag

XX

X

L

3FF

H(3)

Reset Right

INTR Flag

XX

X

L(3)

L

X

3FE

X

Set Left

INTL Flag

XL

L

3FE

H(2)

X

XXX

Reset Left

INTL Flag

2689 tbl 14

Inputs

Outputs

Function

CEL

CER

A0L-A9L

A0R-A9R

BUSYL(1)

BUSYR(1)

X

NO MATCH

H

Normal

H

X

MATCH

H

Normal

X

H

MATCH

H

Normal

L

MATCH

(2)

Write Inhibit

(3)

2689 tbl 15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7140SA25PFGB | HIGH SPEED 1K X 8 DUAL-PORT STATIC SRAM |

| IDT7140SA25PFGI | HIGH SPEED 1K X 8 DUAL-PORT STATIC SRAM |

| IDT7140SA25TFG | HIGH SPEED 1K X 8 DUAL-PORT STATIC SRAM |

| IDT7140SA25TFGB | HIGH SPEED 1K X 8 DUAL-PORT STATIC SRAM |

| IDT7140SA25TFGI | HIGH SPEED 1K X 8 DUAL-PORT STATIC SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 7140LA25JI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 7140LA25JI8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 7140LA25PF | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 7140LA25PF8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 7140LA25PFG | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。