- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293961 > 571MLF (INTEGRATED DEVICE TECHNOLOGY INC) 571 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 PDF資料下載

參數(shù)資料

| 型號: | 571MLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 571 SERIES, PLL BASED CLOCK DRIVER, 2 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO8 |

| 封裝: | 0.150 INCH, ROHS COMPLIANT, SOIC-8 |

| 文件頁數(shù): | 1/7頁 |

| 文件大?。?/td> | 179K |

| 代理商: | 571MLF |

DATASHEET

LOW PHASE NOISE ZERO DELAY BUFFER

ICS571

IDT / ICS LOW PHASE NOISE ZERO DELAY BUFFER

1

ICS571

REV H 051310

Description

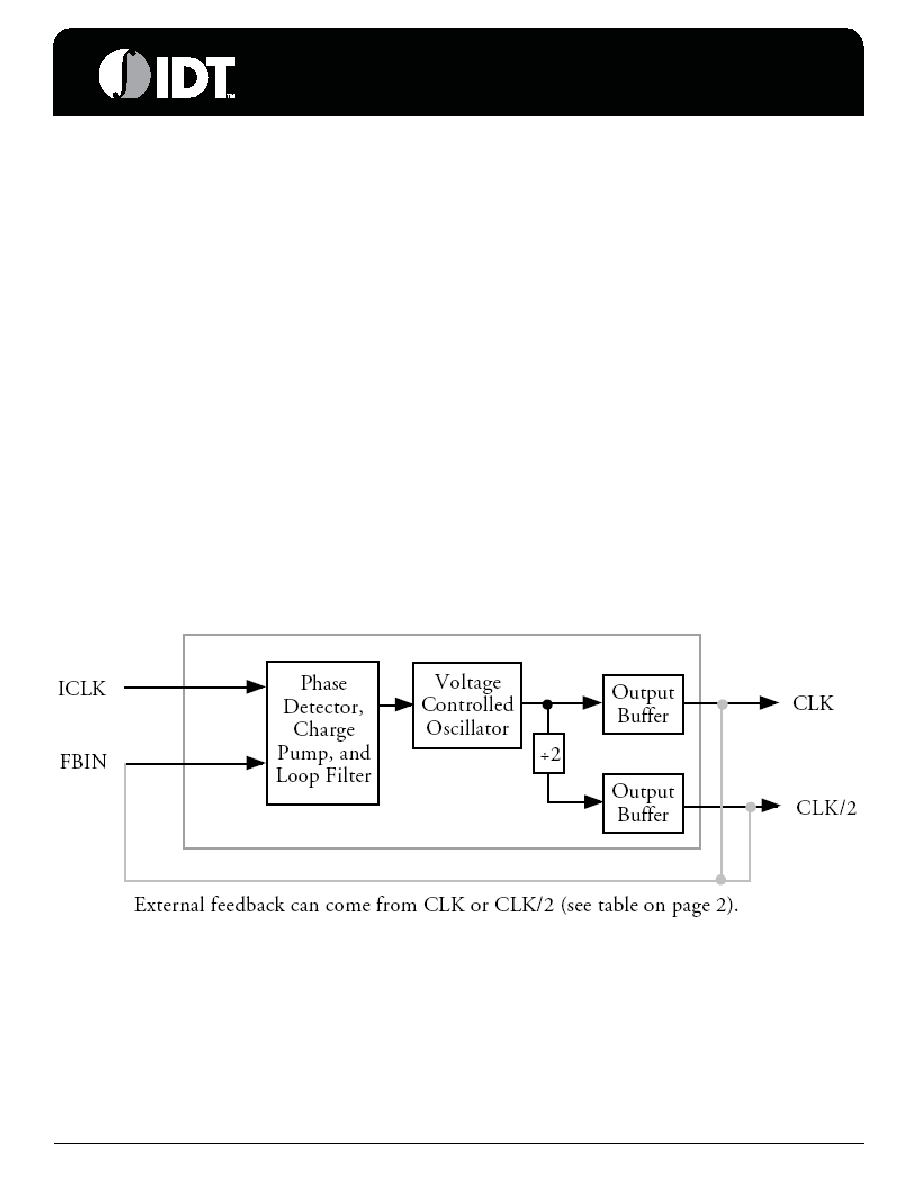

The ICS571 is a high speed, high output drive, low phase

noise Zero Delay Buffer (ZDB) which integrates IDT’s

proprietary analog/digital Phase Locked Loop (PLL)

techniques. IDT introduced the world standard for these

devices in 1992 with the debut of the AV9170, and updated

that with the ICS570. The ICS571, part of IDT’s

ClockBlocks family, was designed to operate at higher

frequencies, with faster rise and fall times, and with lower

phase noise. The zero delay feature means that the rising

edge of the input clock aligns with the rising edges of both

outputs, giving the appearance of no delay through the

device. There are two outputs on the chip, one being a

low-skew divide by two of the other.

The chip is ideal for synchronizing outputs in a large variety

of systems, from personal computers to data

communications to video. By allowing offchip feedback

paths, the ICS571 can eliminate the delay through other

devices. The use of dividers in the feedback path will enable

the part to multiply by more than two.

Features

Packaged in 8-pin SOIC (Pb free)

Can function as low phase noise x2 multiplier

Low skew outputs. One is ÷2 of other

Input clock frequency up to 160 MHz at 3.3 V

Phase noise of better than -100 dBc/Hz from 1 kHz to 1

MHz offset from carrier

Can recover poor input clock duty cycle

Output clock duty cycle of 45/55 at 3.3 V

High drive strength for >100 MHz outputs

Full CMOS clock swings with 25 mA drive capability at

TTL levels

Advanced, low power CMOS process

Operating voltages of 3.0 to 5.5 V

Block Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5745884-2 | 50 CONTACT(S), FEMALE, D SUBMINIATURE CONNECTOR, RECEPTACLE |

| 57461-001-LF | 11 CONTACT(S), FEMALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SURFACE MOUNT, JACK |

| 57461-001 | 11 CONTACT(S), FEMALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SURFACE MOUNT, JACK |

| 57468-001 | 11 CONTACT(S), MALE, STRAIGHT TELECOM AND DATACOM CONNECTOR, SOLDER |

| 57468-002 | 11 CONTACT(S), MALE, STRAIGHT TELECOM AND DATACOM CONNECTOR, SOLDER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 571MLFT | 功能描述:時鐘緩沖器 LOW PHASE NOISE ZERO DELAY BUFFER RoHS:否 制造商:Texas Instruments 輸出端數(shù)量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 571MMA000343DG | 制造商:Silicon Laboratories Inc 功能描述:CONTROLLED OSCILLATOR 10MHZ VCXO LVPECL 6-PIN SMD - Trays |

| 571MMB000107DG | 制造商:Silicon Laboratories Inc 功能描述:CONTROLLED OSCILLATOR 10MHZ VCXO LVPECL 6-PIN SMD - Trays |

| 571MMB000420DG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 571N001B | 制造商:LG Corporation 功能描述:JACK D=3.5 W/NUT |

發(fā)布緊急采購,3分鐘左右您將得到回復。