- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358631 > 376 (Intel Corp.) DIODE SCHOTTKY DUAL-DUAL SERIES 30V 200mW 0.38V-vf 200mA-IFM 1mA-IF 0.2uA-IR SOT-363 3K/REEL PDF資料下載

參數(shù)資料

| 型號: | 376 |

| 廠商: | Intel Corp. |

| 英文描述: | DIODE SCHOTTKY DUAL-DUAL SERIES 30V 200mW 0.38V-vf 200mA-IFM 1mA-IF 0.2uA-IR SOT-363 3K/REEL |

| 中文描述: | 376TM,高性能32位嵌入式處理器 |

| 文件頁數(shù): | 6/95頁 |

| 文件大?。?/td> | 1293K |

| 代理商: | 376 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁

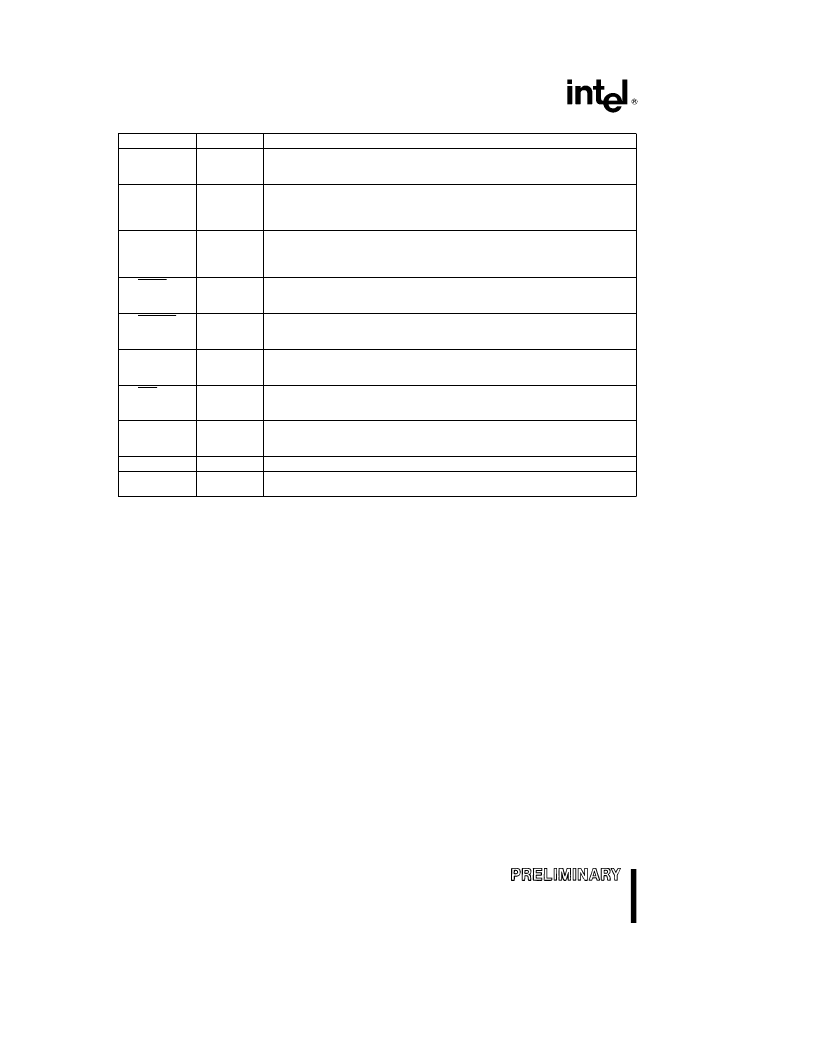

376 EMBEDDED PROCESSOR

Symbol

HLDA

Type

O

Name and Function

BUS HOLD ACKNOWLEDGE

output indicates that the 80376 has

surrendered control of its local bus to another bus master. See

Bus

Arbitration Signals

in Section 4.1 for additional information.

INTERRUPT REQUEST

is a maskable input that signals the 80376 to

suspend execution of the current program and execute an interrupt

acknowledge function. See

Interrupt Signals

in Section 4.1 for

additional information.

NON-MASKABLE INTERRUPT REQUEST

is a non-maskable input

that signals the 80376 to suspend execution of the current program

and execute an interrupt acknowledge function. See

Interrupt Signals

in Section 4.1 for additional information.

BUSY

signals a busy condition from a processor extension. See

Coprocessor Interface Signals

in Section 4.1 for additional

information.

ERROR

signals an error condition from a processor extension. See

Coprocessor Interface Signals

in Section 4.1 for additional

information.

PROCESSOR EXTENSION REQUEST

indicates that the processor

extension has data to be transferred by the 80376. See

Coprocessor

Interface Signals

in Section 4.1 for additional information.

FLOAT,

when active, forces all bidirectional and output signals,

including HLDA, to the float condition. FLOAT is not available on the

PGA package. See

Float

for additional information.

NO CONNECT

should always remain unconnected. Connection of a

N/C pin may cause the processor to malfunction or be incompatible

with future steppings of the 80376.

SYSTEM POWER

provides the

a

5V nominal D.C. supply input.

SYSTEM GROUND

provides 0V connection from which all inputs and

outputs are measured.

INTR

I

NMI

I

BUSY

I

ERROR

I

PEREQ

I

FLT

I

N/C

D

V

CC

V

SS

I

I

2.0 ARCHITECTURE OVERVIEW

The 80376 supports the protection mechanisms

needed by sophisticated multitasking embedded

systems and real-time operating systems. The use

of these protection mechanisms is completely op-

tional. For embedded applications not needing pro-

tection, the 80376 can easily be configured to pro-

vide a 16 Mbyte physical address space.

Instruction pipelining, high bus bandwidth, and a

very high performance ALU ensure short average

instruction

execution

times

throughput. The 80376 is capable of execution at

sustained rates of 2.5–3.0 million instructions per

second.

and

high

system

The 80376 offers on-chip testability and debugging

features. Four break point registers allow conditional

or unconditional break point traps on code execution

or data accesses for powerful debugging of even

ROM based systems. Other testability features in-

clude self-test and tri-stating of output buffers during

RESET.

The Intel 80376 embedded processor consists of a

central processing unit, a memory management unit

and a bus interface. The central processing unit con-

sists of the execution unit and instruction unit. The

execution unit contains the eight 32-bit general reg-

isters which are used for both address calculation

and data operations and a 64-bit barrel shifter used

to speed shift, rotate, multiply, and divide operations.

The instruction unit decodes the instruction opcodes

and stores them in the decoded instruction queue

for immediate use by the execution unit.

The Memory Management Unit (MMU) consists of a

segmentation and protection unit. Segmentation al-

lows the managing of the logical address space by

providing an extra addressing component, one that

allows easy code and data relocatability, and effi-

cient sharing.

The protection unit provides four levels of protection

for isolating and protecting applications and the op-

erating system from each other. The hardware en-

forced protection allows the design of systems with

a high degree of integrity and simplifies debugging.

Finally, to facilitate high performance system hard-

ware designs, the 80376 bus interface offers ad-

dress pipelining and direct Byte Enable signals for

each byte of the data bus.

6

相關PDF資料 |

PDF描述 |

|---|---|

| 37LV128-TISN | DIODE ZENER SINGLE 200mW 2.7Vz 5mA-Izt 0.0741 20uA-Ir 1 SOD-323 3K/REEL |

| 37LV128-TL | DIODE ZENER SINGLE 150mW 2.7Vz 5mA-Izt 0.074 20uA-Ir 1 SOD-523 3K/REEL |

| 37LV128-TP | DIODE/SM, ZEN 30V .5MA 0.41W +/-5% SOD-123 |

| 37LV128-TSN | 36K, 64K, and 128K Serial EPROM Family |

| 37LV128-IL | 36K, 64K, and 128K Serial EPROM Family |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 376 | 制造商:Pro-Signal 功能描述:; Supply Voltage:28VDC; Lamp Base Type:M |

| 37-6.8 | 制造商:Distributed By MCM 功能描述:Resistor 1/2W 6.8 Ohm Flameproof, Bag of 20 制造商:MCM 功能描述:1/2 Watt Flameproof Resistors, Resistance: 6.8 Ohm, Tolerance: 5 %, Quantity: 20 per bag |

| 37-6.8K | 制造商:Distributed By MCM 功能描述:Resistor 1/2W 6.8K Ohm Flameproof, Bag of 20 制造商:MCM 功能描述:RESISTOR 1/2W 6.8K OHM FLAMPRF20 PER BAG |

| 376/377-1ZM | 制造商:Rayovac 功能描述:SILVER ELECTRONIC BTRY 1PK MERCURY FREE |

發(fā)布緊急采購,3分鐘左右您將得到回復。