- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371436 > 29109BRA (HARRIS SEMICONDUCTOR) 16K x 1 Asynchronous CMOS Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | 29109BRA |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | DRAM |

| 英文描述: | 16K x 1 Asynchronous CMOS Static RAM |

| 中文描述: | 16K X 1 STANDARD SRAM, 70 ns, CDIP20 |

| 文件頁數(shù): | 4/7頁 |

| 文件大?。?/td> | 41K |

| 代理商: | 29109BRA |

6-4

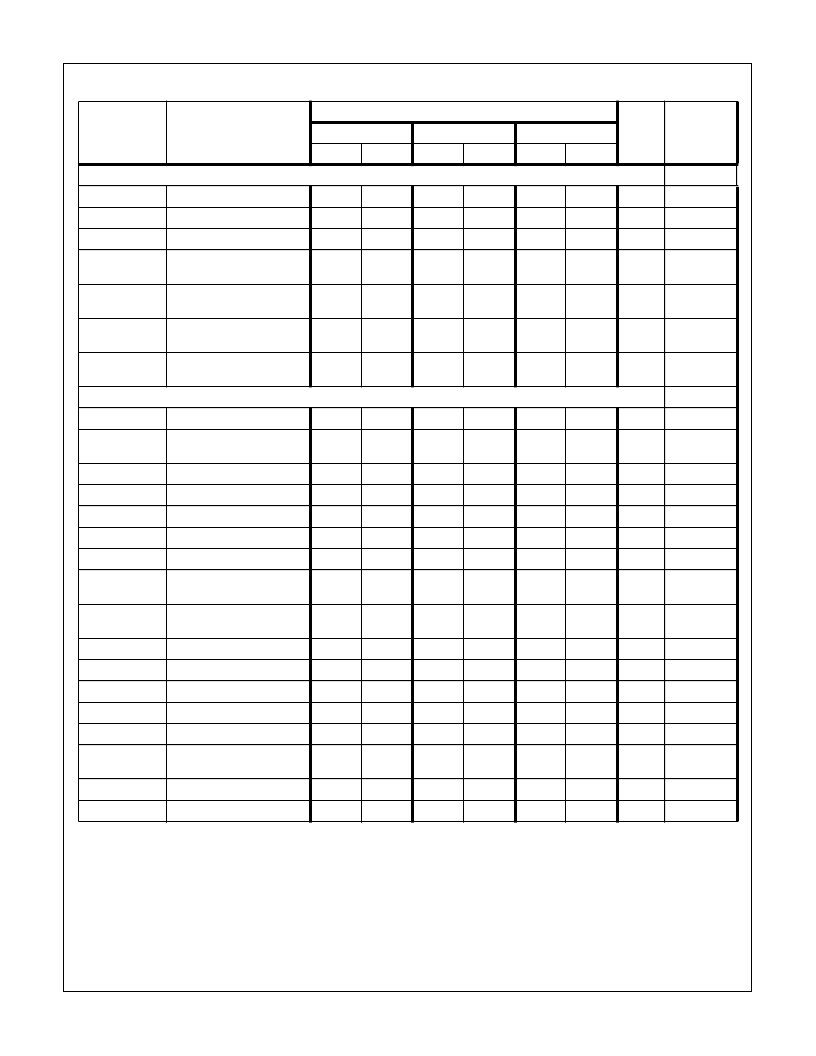

AC Electrical Specifications

V

CC

= 5V 10%,T

A

= -40

o

C to +85

o

C (HM-65262B-9, HM-65262-9, HM-65262C-9)

SYMBOL

PARAMETER

LIMITS

UNITS

TEST

CONDITIONS

HM-65262B-9

HM-65262-9

HM-65262C-9

MIN

MAX

MIN

MAX

MIN

MAX

READ CYCLE

(1)

TAVAX

Read/Cycle Time

70

-

85

-

85

-

ns

(Notes 1, 3)

(2)

TAVQV

Address Access Time

-

70

-

85

-

85

ns

(Notes 1, 3)

(3)

TELQV

Chip Enable Access Time

-

70

-

85

-

85

ns

(Notes 1, 3)

(4)

TELQX

Chip Enable Output Enable

Time

5

-

5

-

5

-

ns

(Notes 2, 3)

(5)

TEHQX

Chip Disable Output Hold

Time

5

-

5

-

5

-

ns

(Notes 2, 3)

(6)

TAXQX

Address Invalid Output Hold

Time

5

-

5

-

5

-

ns

(Notes 2, 3)

(7)

TEHQZ

Chip Enable Output Disable

Time

-

30

-

30

-

30

ns

(Notes 2, 3)

WRITE CYCLE

(8)

TAVAX

Write Cycle Time

70

-

85

-

85

-

ns

(Notes 1, 3)

(9)

TELWH

Chip Selection to End of

Write

55

-

65

-

65

-

ns

(Notes 1, 3)

(10)

TWLWH

Write Enable Pulse Width

40

-

45

-

45

-

ns

(Notes 1, 3)

(11)

TAVWL

Address Setup Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(12)

TWHAX

Address Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(13)

TDVWH

Data Setup Time

30

-

35

-

35

-

ns

(Notes 1, 3)

(14)

TWHDX

Data Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(15)

TWLQZ

Write Enable Output Disable

Time

-

30

-

30

-

30

ns

(Notes 2, 3)

(16)

TWHQX

Write Disable Output Enable

Time

0

-

0

-

0

-

ns

(Notes 2, 3)

(17)

TAVWH

Address Valid to End of Write

55

-

65

-

65

-

ns

(Notes 1, 3)

(18)

TAVEL

Address Setup Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(19)

TEHAX

Address Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

(20)

TAVEH

Address Valid to End of Write

55

-

65

-

65

-

ns

(Notes 1, 3)

(21)

TELEH

Enable Pulse Width

55

-

65

-

65

-

ns

(Notes 1, 3)

(22)

TWLEH

Write Enable Pulse Setup

Time

40

-

45

-

45

-

ns

(Notes 1, 3)

(23)

TDVEH

Chip Setup Time

30

-

35

-

35

0

ns

(Notes 1, 3)

(24)

TEHDX

Data Hold Time

0

-

0

-

0

-

ns

(Notes 1, 3)

NOTES:

1. Input pulse levels: 0 to 3.0V; Input rise and fall times: 5ns (max); Input and output timing reference level: 1.5V; Output load: 1 TTL gate

equivalent and C

L

= 50pF (min) - for C

L

greater than 50pF, access time is derated by 0.15ns per pF.

2. Tested at initial design and after major design changes.

3. V

CC

= 4.5 and 5.5V.

HM-65262

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 2910 | 10 MHz BIPOLAR LOGARITHMIC AMPLIFIER |

| 29110BJA | 2K x 8 Asynchronous CMOS Static RAM |

| 29104BJA | 2K x 8 Asynchronous CMOS Static RAM |

| 2912A | PCM TRANSMIT/RECEIVE FILTER |

| 2916 | FAN 12VDC FLIGHT II 80 FE12H3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 29109E3 | 制造商:VISHAY 制造商全稱:Vishay Siliconix 功能描述:Aluminum Capacitors Axial High Temperature, DIN-Based |

| 2910A/BQA | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商: 功能描述: 制造商:undefined 功能描述: |

| 2910A/BZC | 制造商:Rochester Electronics LLC 功能描述: |

| 2910ADC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 2910ADM | 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。