- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384067 > μPD789415 (NEC Corp.) 8 Bit Single Chip Microcontrollers(8位單片微控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | μPD789415 |

| 廠商: | NEC Corp. |

| 英文描述: | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

| 中文描述: | 8位單片機(jī)微控制器(8位單片微控制器) |

| 文件頁(yè)數(shù): | 80/126頁(yè) |

| 文件大小: | 590K |

| 代理商: | ΜPD789415 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)當(dāng)前第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)

80

μ

PD789415, 789416, 789417

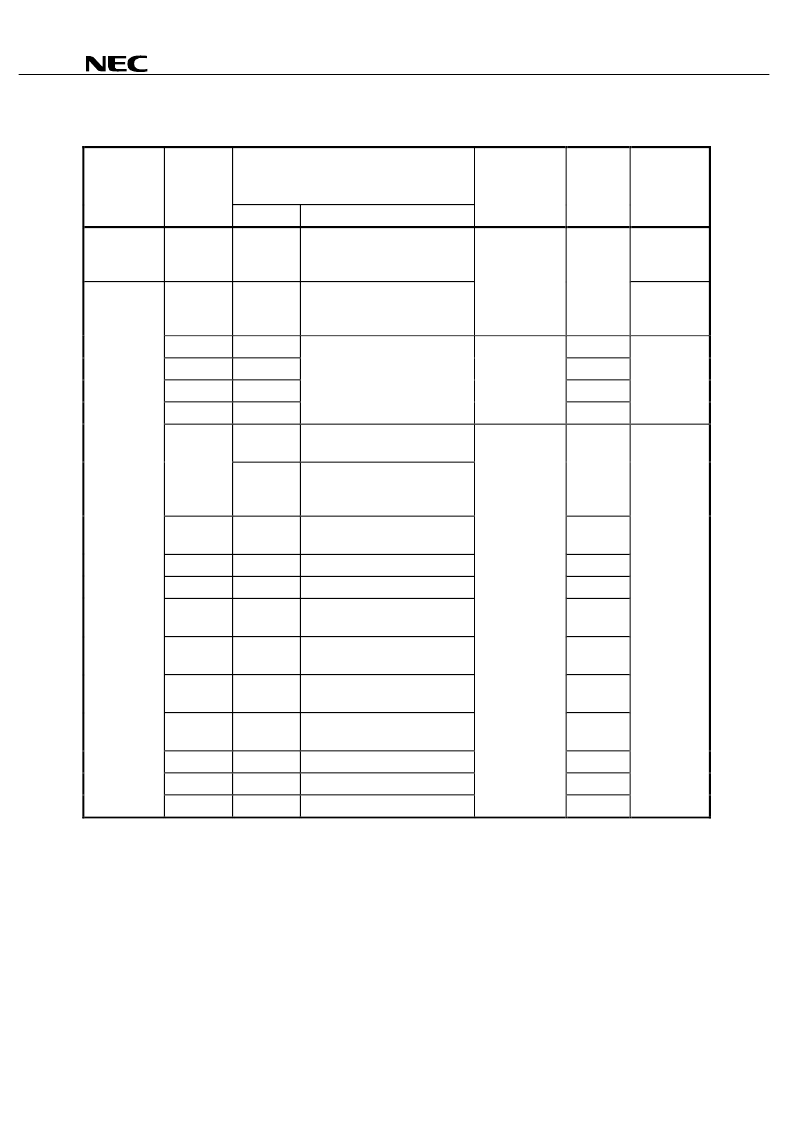

Table 6-1. Interrupt Sources

Interrupt type

Default

priority

Note 1

Interrupt source

Internal/external

Name

Trigger

Nonmaskable

interrupt

INTWDT

Watchdog timer overflow

(when watchdog timer mode 1 is

selected)

Internal

0004H

(A)

Maskable

0

INTWDT

Watchdog timer overflow

(when the interval timer mode is

selected)

(B)

1

INTP0

Pin input edge detection

External

0006H

(C)

2

INTP1

0008H

3

INTP2

000AH

4

INTP3

000CH

5

INTSR

End of UART reception on serial

interface channel 0

Internal

000EH

(B)

INTCSI0

End of three-wire SIO transfer

reception on serial interface

channel 0

6

INTST

End of UART transmission on

serial interface channel 0

0010H

7

INTWT

Clock timer interrupt

0012H

8

INTWTI

Interval timer interrupt

0014H

9

INTTM0

Generation of match signal for

8-bit timer/event counter 0

0016H

10

INTTM1

Generation of match signal for

8-bit timer/event counter 1

0018H

11

INTTM2

Generation of match signal for

8-bit timer counter 2

001AH

12

INTTM5

Generation of match signal for 16-

bit timer counter 5

001CH

13

INTKR

Key return signal detection

001EH

14

INTAD

A/D conversion completion signal

0020H

15

INTCMP

Comparator signal

0022H

Notes 1.

The default priority regulates which maskable interrupt is higher, when two or more maskable interrupts

are requested simultaneously. Zero signifies the highest priority, while 15 is the lowest.

2.

Basic configuration types (A), (B), and (C) correspond to (A), (B), and (C) in Figure 6-1, respectively.

Vector Basic

table

address type

configuration

Note 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD789416 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

| μPD789800 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

| μPD789830 | 8 Bit Single Chip Microcontrollers(8 位微控制器) |

| μPD78F9831 | 8 Bit Single Chip Microcontrollers(8 位微控制器) |

| μPD78F0974 | 8 Bit Single Chip Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD78F0134 | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134(A) | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134(A1) | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134A | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134A1 | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。