- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384067 > μPD789186 (NEC Corp.) 8 Bit Single Chip Microcontrollers(8 位單片微控制器) PDF資料下載

參數(shù)資料

| 型號: | μPD789186 |

| 廠商: | NEC Corp. |

| 英文描述: | 8 Bit Single Chip Microcontrollers(8 位單片微控制器) |

| 中文描述: | 8位單片機微控制器(8位單片微控制器) |

| 文件頁數(shù): | 21/146頁 |

| 文件大小: | 630K |

| 代理商: | ΜPD789186 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁

Preliminary Product Information

21

μ

PD789186, 789187, 789196, 789197

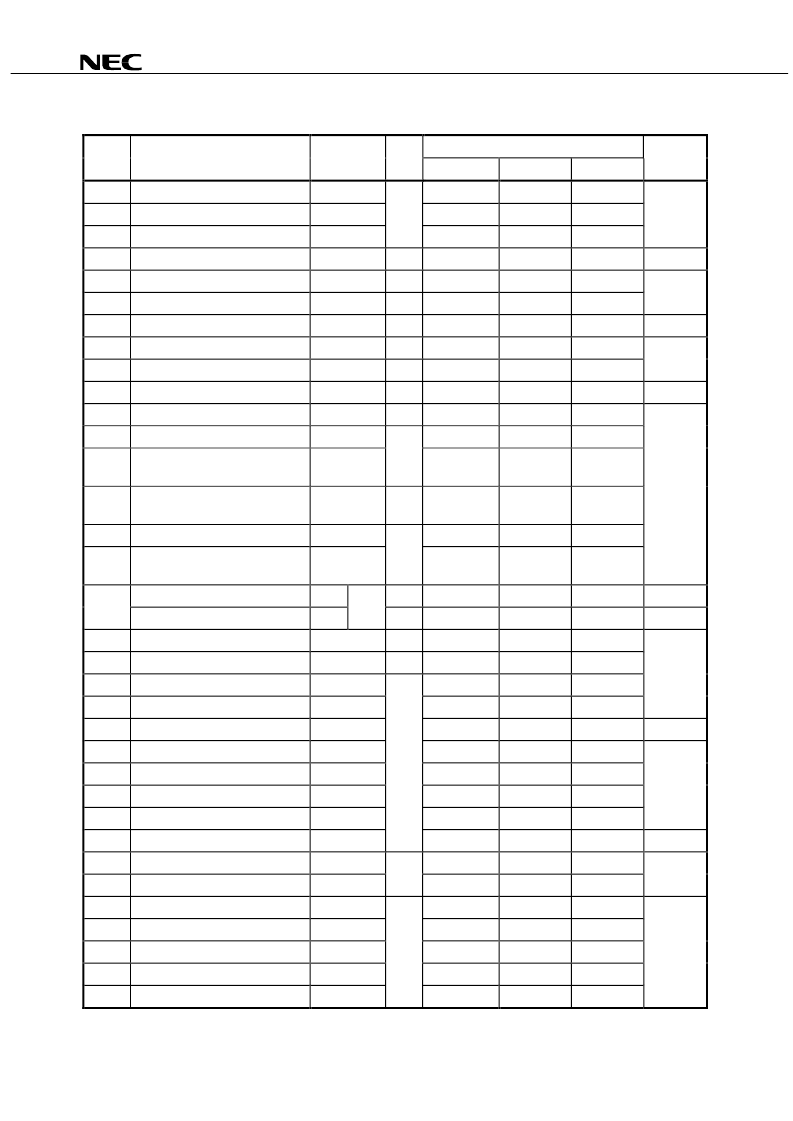

Table 4-1. Special Function Registers (2/3)

Address Special function register (SFR) name

Symbol

R/W

Number of bits manipulated simultaneously

When reset

1 bit

8 bits

16 bits

FF48H

16-bit timer mode control register 90

TMC90

R/W

{

{

00H

FF49H

Buzzer output control register 90

BZC90

{

{

FF4AH

Clock timer mode control register

WTM

{

{

FF50H

8-bit compare register 80

CR80

W

{

Undefined

FF51H

8-bit timer register 80

TM80

R

{

00H

FF53H

8-bit timer mode control register 80

TMC80

R/W

{

{

FF54H

8-bit compare register 81

CR81

W

{

Undefined

FF55H

8-bit timer register 81

TM81

R

{

00H

FF57H

8-bit timer mode control register 81

TMC81

R/W

{

{

FF58H

8-bit compare register 82

CR82

W

{

Undefined

FF59H

8-bit timer register 82

TM82

R

{

00H

FF5BH

8-bit timer mode control register 82

TMC82

R/W

{

{

FF70H

Asynchronous serial interface mode

register 20

ASIM20

{

{

FF71H

Asynchronous serial interface

status register 20

ASIS20

R

{

FF72H

Serial operation mode register 20

CSIM20

R/W

{

{

FF73H

Baud rate generator control register

20

BRGC20

{

{

FF74H

Transmission shift register 20

TXS20

SIO20

W

{

FFH

Reception buffer register 20

RXB20

R

{

Undefined

FF78H

SMB control register 0

SMBC0

R/W

{

{

00H

FF79H

SMB status register 0

SMBS0

R

{

{

FF7AH

SMB clock selection register 0

SMBCL0

R/W

{

{

FF7BH

SMB slave address register 0

SMBSVA0

{

{

FF7CH

SMB mode register 0

SMBM0

{

{

20H

FF7DH

SMB input level setting register 0

SMBVI0

{

{

00H

FF7EH

SMB shift register 0

SMB0

{

{

FF80H

A/D converter mode register 0

ADM0

{

{

FF84H

A/D input selection register 0

ADS0

{

{

FFCCH

EEPROM write control register 0

EEWC0

{

{

04H

FFD0H

Multiplication data register A0

MRA0

W

{

{

Undefined

FFD1H

Multiplication data register B0

MRB0

{

{

FFD2H

Multiplier control register 0

MULC0

R/W

{

{

00H

FFDFH

Low-voltage indicator register 0

LVI0

{

{

FFE0H

Interrupt request flag register 0

IF0

{

{

FFE1H

Interrupt request flag register 1

IF1

{

{

FFE2H

Interrupt request flag register 2

IF2

{

{

相關PDF資料 |

PDF描述 |

|---|---|

| μPD789198 | 8 Bit Single Chip Microcontrollers(8 位單片微控制器) |

| μPD789216Y | 8 Bit Single Chip Microcontrollers(8 位單片微控制器) |

| μPD789217Y | 8 Bit Single Chip Microcontrollers(8 位單片微控制器) |

| μPD789405 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

| μPD789407 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PD78F0134 | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134(A) | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134(A1) | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134A | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134A1 | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復。