- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16606 > XR20M1280L24-0A-EB (Exar Corporation)EVAL BOARD FOR XR20M1280 PDF資料下載

參數(shù)資料

| 型號(hào): | XR20M1280L24-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 61/63頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR XR20M1280 |

| 產(chǎn)品培訓(xùn)模塊: | XR21V141x Full-Speed USB UART Family UARTs with Integrated Level Shifters |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 主要目的: | 接口,UART |

| 已用 IC / 零件: | XR20M1280L24 |

| 已供物品: | 板 |

| 其它名稱: | 1016-1632 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)當(dāng)前第61頁(yè)第62頁(yè)第63頁(yè)

XR20M1280

7

REV. 1.0.0

I2C/SPI UART WITH 128-BYTE FIFO AND INTEGRATED LEVEL SHIFTERS

1.0 FUNCTIONAL DESCRIPTIONS

1.1

CPU Interface

The XR20M1280 can operate with either an I2C-bus interface or an SPI interface. The CPU interface is

selected via the I2C/SPI# input pin.

1.1.1

I2C-bus Interface

The I2C-bus interface is compliant with the Standard-mode and Fast-mode I2C-bus specifications. The I2C-bus

interface consists of two lines: serial data (SDA) and serial clock (SCL). In the Standard-mode, the serial clock

and serial data can go up to 100 kbps and in the Fast-mode, the serial clock and serial data can go up to 400

kbps. The first byte sent by an I2C-bus master contains a start bit (SDA transition from HIGH to LOW when

SCL is HIGH), 7-bit slave address and whether it is a read or write transaction. The next byte is the sub-

address that contains the address of the register to access. The XR20M1280 responds to each write with an

acknowledge (SDA driven LOW by XR20M1280 for one clock cycle when SCL is HIGH). If the TX FIFO is full,

the XR20M1280 will respond with a negative acknowledge (SDA driven HIGH by XR20M1280 for one clock

cycle when SCL is HIGH) when the CPU tries to write to the TX FIFO. The last byte sent by an I2C-bus master

contains a stop bit (SDA transition from LOW to HIGH when SCL is HIGH). See Figures 3 - 5 below. For

complete details, see the I2C-bus specifications.

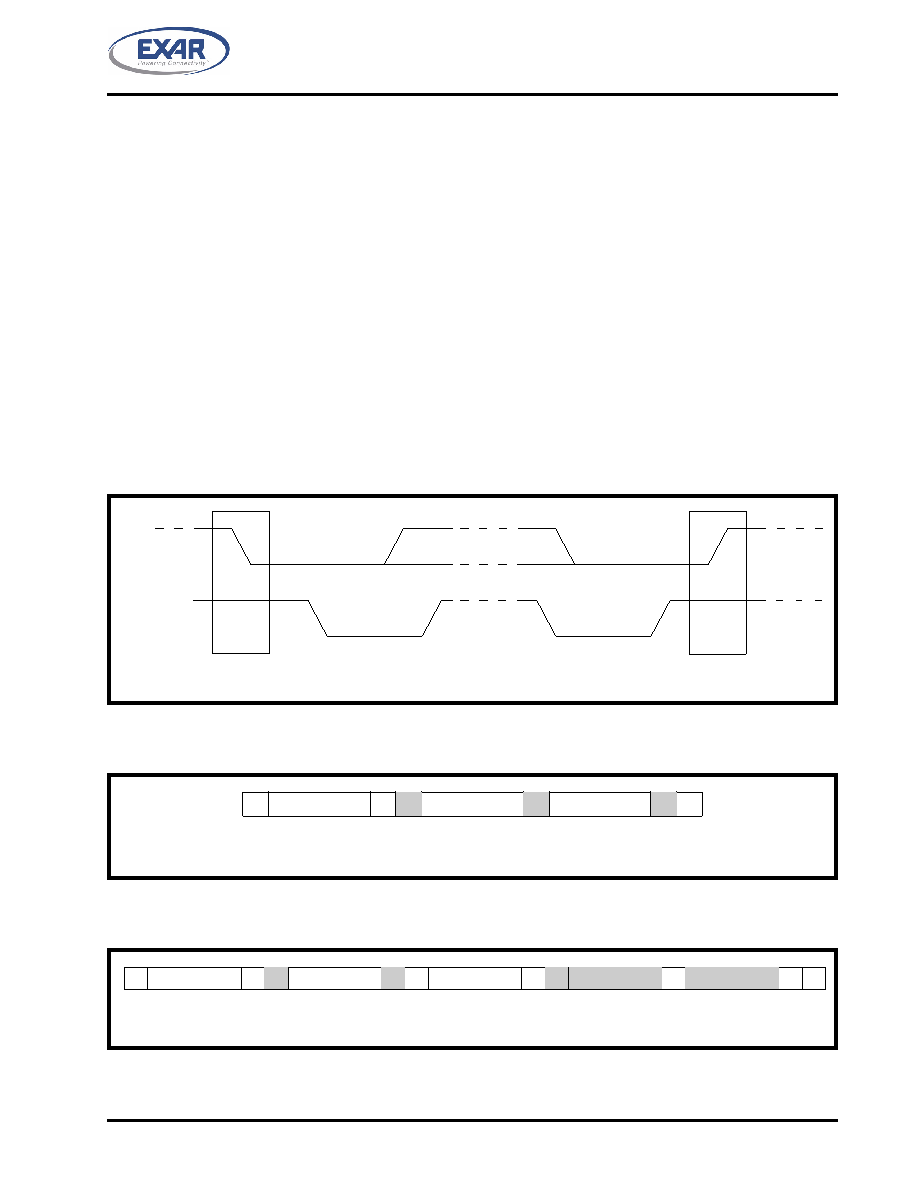

FIGURE 3. I C START AND STOP CONDITIONS

SDA

SCL

S

P

START condition

STOP condition

FIGURE 4. MASTER WRITES TO SLAVE (XR20M1280)

SW

A

AP

SLAVE

ADDRESS

REGISTER

ADDRESS

nDATA

White block: host to UART

Grey block: UART to host

FIGURE 5. MASTER READS FROM SLAVE (XR20M1280)

SW

A

AR

SLAVE

ADDRESS

REGISTER

ADDRESS

White block: host to UART

Grey block: UART to host

A

S

SLAVE

ADDRESS

nDATA

ANA

P

LAST DATA

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Q5-2X-1/8-01-SS200M | HEATSHK DL WL Q52X 1/8"X200M BLK |

| V150B5E150B3 | CONVERTER MOD DC/DC 5V 150W |

| RCC10DCMT-S288 | CONN EDGECARD 20POS .100 EXTEND |

| EBC10DREN-S93 | CONN EDGECARD 20POS .100 EYELET |

| V150B48E150BL | CONVERTER MOD DC/DC 48V 150W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR20M1280L24-0B-EB | 功能描述:UART 接口集成電路 EVAL F/ M1280 QFN24 SPI INTERFACE RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR20M1280L32-0A-EB | 功能描述:UART 接口集成電路 EVAL F/M1280 QFN32 I2C INTERFACE RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR20M1280L32-0B-EB | 功能描述:UART 接口集成電路 EVAL F/M1280 QFN32 SPI INTERFACE RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR20M1280L40-0A-EB | 功能描述:UART 接口集成電路 EVAL F/M1280 QFN40 I2C INTERFACE RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR20M1280L40-0B-EB | 功能描述:UART 接口集成電路 EVAL F/M1280 QFN40 SPI INTERFACE RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。