- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4054 > XCS05-3PC84C (Xilinx Inc)IC FPGA 5V C-TEMP 84-PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | XCS05-3PC84C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 40/83頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 5V C-TEMP 84-PLCC |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan® |

| LAB/CLB數(shù): | 100 |

| 邏輯元件/單元數(shù): | 238 |

| RAM 位總計(jì): | 3200 |

| 輸入/輸出數(shù): | 61 |

| 門數(shù): | 5000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 84-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 84-PLCC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

45

Product Specification

R

Product Obsolete/Under Obsolescence

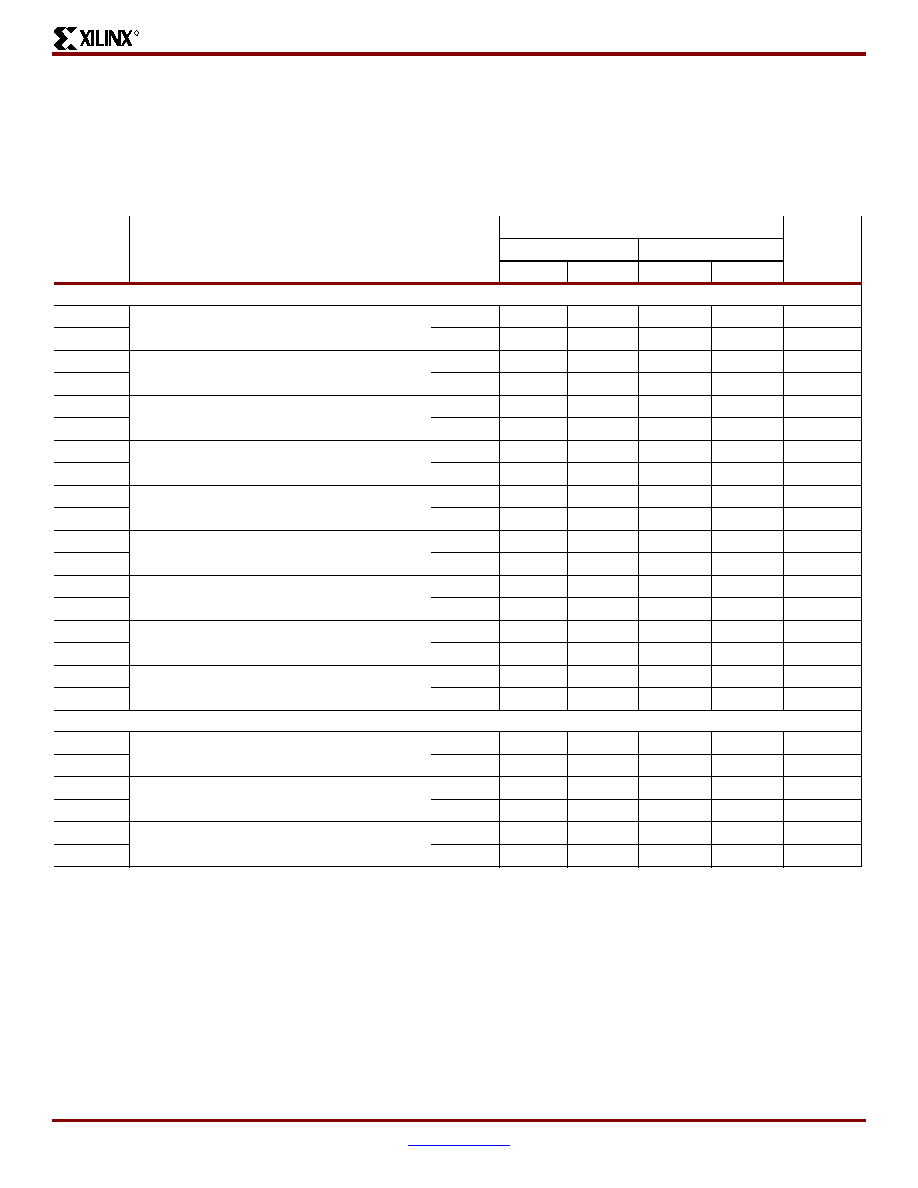

Spartan Family CLB RAM Synchronous (Edge-Triggered) Write Operation Guidelines

All devices are 100% functionally tested. Internal timing

parameters are derived from measuring internal test pat-

terns. Listed below are representative values. For more

specific, more precise, and worst-case guaranteed data,

use the values reported by the static timing analyzer (TRCE

in the Xilinx Development System) and back-annotated to

the simulation netlist. All timing parameters assume

tion temperature). Values apply to all Spartan devices and

are expressed in nanoseconds unless otherwise noted.

Symbol

Single Port RAM

Size(1)

Speed Grade

Units

-4

-3

Min

Max

Min

Max

Write Operation

TWCS

Address write cycle time (clock K period)

16x2

8.0

-

11.6

-

ns

TWCTS

32x1

8.0

-

11.6

-

ns

TWPS

Clock K pulse width (active edge)

16x2

4.0

-

5.8

-

ns

TWPTS

32x1

4.0

-

5.8

-

ns

TASS

Address setup time before clock K

16x2

1.5

-

2.0

-

ns

TASTS

32x1

1.5

-

2.0

-

ns

TAHS

Address hold time after clock K

16x2

0.0

-

0.0

-

ns

TAHTS

32x1

0.0

-

0.0

-

ns

TDSS

DIN setup time before clock K

16x2

1.5

-

2.7

-

ns

TDSTS

32x1

1.5

-

1.7

-

ns

TDHS

DIN hold time after clock K

16x2

0.0

-

0.0

-

ns

TDHTS

32x1

0.0

-

0.0

-

ns

TWSS

WE setup time before clock K

16x2

1.5

-

1.6

-

ns

TWSTS

32x1

1.5

-

1.6

-

ns

TWHS

WE hold time after clock K

16x2

0.0

-

0.0

-

ns

TWHTS

32x1

0.0

-

0.0

-

ns

TWOS

Data valid after clock K

16x2

-

6.5

-

7.9

ns

TWOTS

32x1

-

7.0

-

9.3

ns

Read Operation

TRC

Address read cycle time

16x2

2.6

-

2.6

-

ns

TRCT

32x1

3.8

-

3.8

-

ns

TILO

Data valid after address change (no Write

Enable)

16x2

-

1.2

-

1.6

ns

TIHO

32x1

-

2.0

-

2.7

ns

TICK

Address setup time before clock K

16x2

1.8

-

2.4

-

ns

TIHCK

32x1

2.9

-

3.9

-

ns

Notes:

1.

Timing for 16 x 1 RAM option is identical to 16 x 2 RAM timing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MPC862PCZQ80B | IC MPU PWRQUICC 80MHZ 357-PBGA |

| IDT7024L15JG8 | IC SRAM 64KBIT 15NS 84PLCC |

| IDT7024L15J8 | IC SRAM 64KBIT 15NS 84PLCC |

| IDT7133LA25PFGI | IC SRAM 32KBIT 25NS 100TQFP |

| IDT7143LA25PFI | IC SRAM 32KBIT 25NS 100TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS05-3PC84I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3PQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3PQ100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3PQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3PQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。