- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄375014 > XCR5128-15TQ128C (Xilinx, Inc.) 128 Macrocell CPLD PDF資料下載

參數(shù)資料

| 型號(hào): | XCR5128-15TQ128C |

| 廠商: | Xilinx, Inc. |

| 英文描述: | 128 Macrocell CPLD |

| 中文描述: | 128個(gè)宏單元CPLD |

| 文件頁(yè)數(shù): | 10/20頁(yè) |

| 文件大小: | 131K |

| 代理商: | XCR5128-15TQ128C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)

R

XCR5128: 128 Macrocell CPLD

DS041 (v1.4) January 19, 2001

www.xilinx.com

1-800-255-7778

10

This product has been discontinued. Please see

www.xilinx.com/partinfo/notify/pdn0007.htm

for details.

JTAG and ISP Interfacing

A number of industry-established methods exist for

JTAG/ISP interfacing with CPLD

’

s and other integrated cir-

cuits. The Xilinx XCR5128 supports the following methods:

PC parallel port

Workstation or PC serial port

Embedded processor

Automated test equipment

Third party programmers

High-End JTAG and ISP tools

A Boundary-Scan Description Language (BSDL) descrip-

tion of the XCR5128 is also available from Xilinx for use in

test program development. For more details on JTAG and

ISP for the XCR5128, refer to the related application note:

JTAG and ISP in Xilinx CPLDs

.

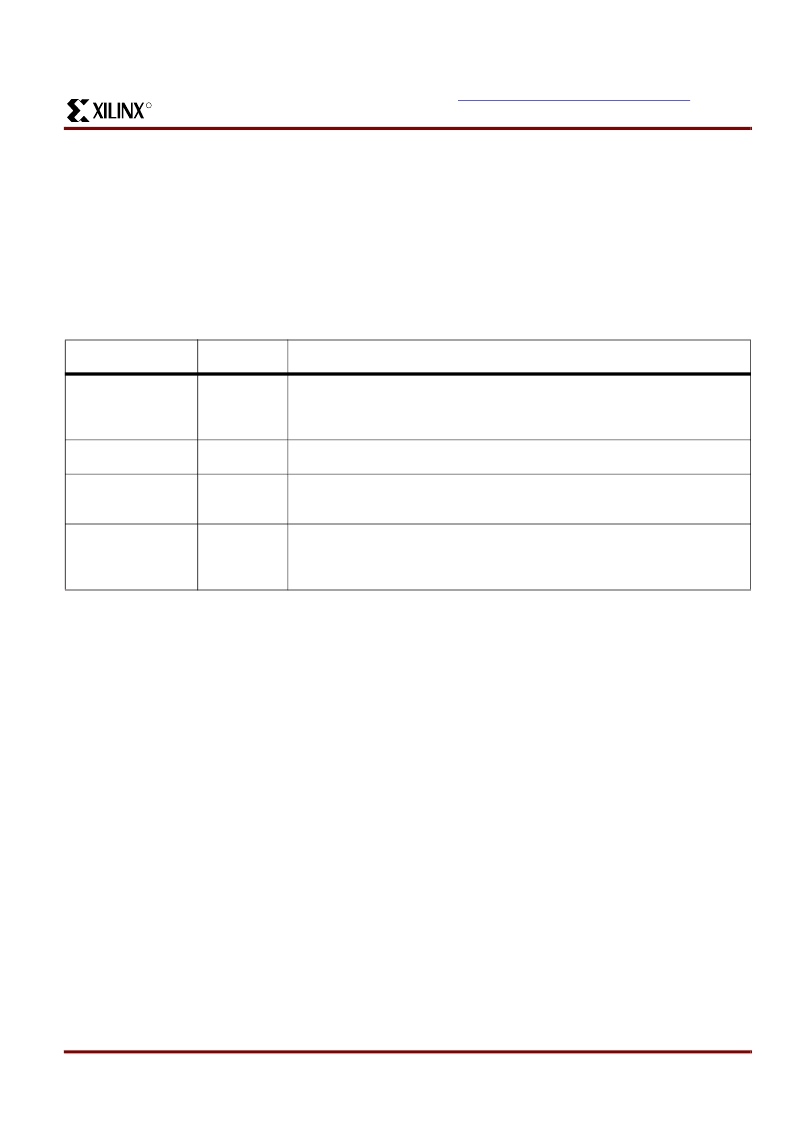

Table 5: Low Level ISP Commands

Instruction

(Register Used)

Enable

(ISP Shift Register)

Instruction

Code

1001

Description

Enables the Erase, Program, and Verify commands. Using the ENABLE instruction

before the Erase, Program, and Verify instructions allows the user to specify the

outputs the device using the JTAG Boundary-Scan SAMPLE/PRELOAD

command.

Erases the entire EEPROM array. The outputs during this operation can be defined

by user by using the JTAG SAMPLE/PRELOAD command.

Programs the data in the ISP Shift Register into the addressed EEPROM row. The

outputs during this operation can be defined by user by using the JTAG

SAMPLE/PRELOAD command.

Transfers the data from the addressed row to the ISP Shift Register. The data can

then be shifted out and compared with the JEDEC file. The outputs during this

operation can be defined by user by using the JTAG SAMPLE/PRELOAD

command.

Erase

(ISP Shift Register)

Program

(ISP Shift Register)

1010

1011

Verify

(ISP Shift Register)

1100

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCR5128-15VQ100C | 128 Macrocell CPLD |

| XCR5128-15VQ100I | 128 Macrocell CPLD |

| XCR5128-7PC84C | 128 Macrocell CPLD |

| XCR5128-7PC84I | 128 Macrocell CPLD |

| XCR5128-7PQ100C | 128 Macrocell CPLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCR5128-15TQ128I | 制造商:XILINX 制造商全稱:XILINX 功能描述:128 Macrocell CPLD |

| XCR5128-15VQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:128 Macrocell CPLD |

| XCR5128-15VQ100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:128 Macrocell CPLD |

| XCR5128-7PC84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:128 Macrocell CPLD |

| XCR5128-7PC84I | 制造商:XILINX 制造商全稱:XILINX 功能描述:128 Macrocell CPLD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。