- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄225572 > XC4VFX100-10FFG1517I (XILINX INC) FPGA, 10544 CLBS, 1028 MHz, PBGA1517 PDF資料下載

參數(shù)資料

| 型號(hào): | XC4VFX100-10FFG1517I |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 10544 CLBS, 1028 MHz, PBGA1517 |

| 封裝: | LEAD FREE, FBGA-1517 |

| 文件頁(yè)數(shù): | 33/58頁(yè) |

| 文件大?。?/td> | 1863K |

| 代理商: | XC4VFX100-10FFG1517I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

Virtex-4 FPGA Data Sheet: DC and Switching Characteristics

DS302 (v3.7) September 9, 2009

Product Specification

39

CLKOUT_FREQ_FX_HF_MS_MIN

CLKFX, CLKFX180

210

MHz

CLKOUT_FREQ_FX_HF_MS_MAX

350

315

300

MHz

Input Clocks (High Frequency Mode)

CLKIN_FREQ_DLL_HF_MS_MIN(6)

CLKIN (using DLL outputs only)(1,3,4,5)

150

MHz

CLKIN_FREQ_DLL_HF_MS_MAX

500

450

400

MHz

CLKIN_FREQ_FX_HF_MS_MIN

CLKIN (using DFS outputs)(2,3,4)

50

MHz

CLKIN_FREQ_FX_HF_MS_MAX(6)

350

315

300

MHz

PSCLK_FREQ_HF_MS_MIN

PSCLK

111

KHz

PSCLK_FREQ_HF_MS_MAX

500

450

400

MHz

Notes:

1.

DLL outputs are used in these instances to describe the outputs: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV.

2.

DFS outputs are used in these instances to describe the outputs: CLKFX and CLKFX180.

3.

When using the DCMs CLKIN_DIVIDE_BY_2 attribute these values should be doubled.

4.

When using a CLKIN frequency > 400 MHz and the DCMs CLKIN_DIVIDE_BY_2 attribute, the CLKIN duty cycle must be within ±5% (45/55 to

55/45).

5.

The DCM must be reset if the clock input clock stops for more than 100 ms.

6.

These values also apply when using both DLL and DFS outputs.

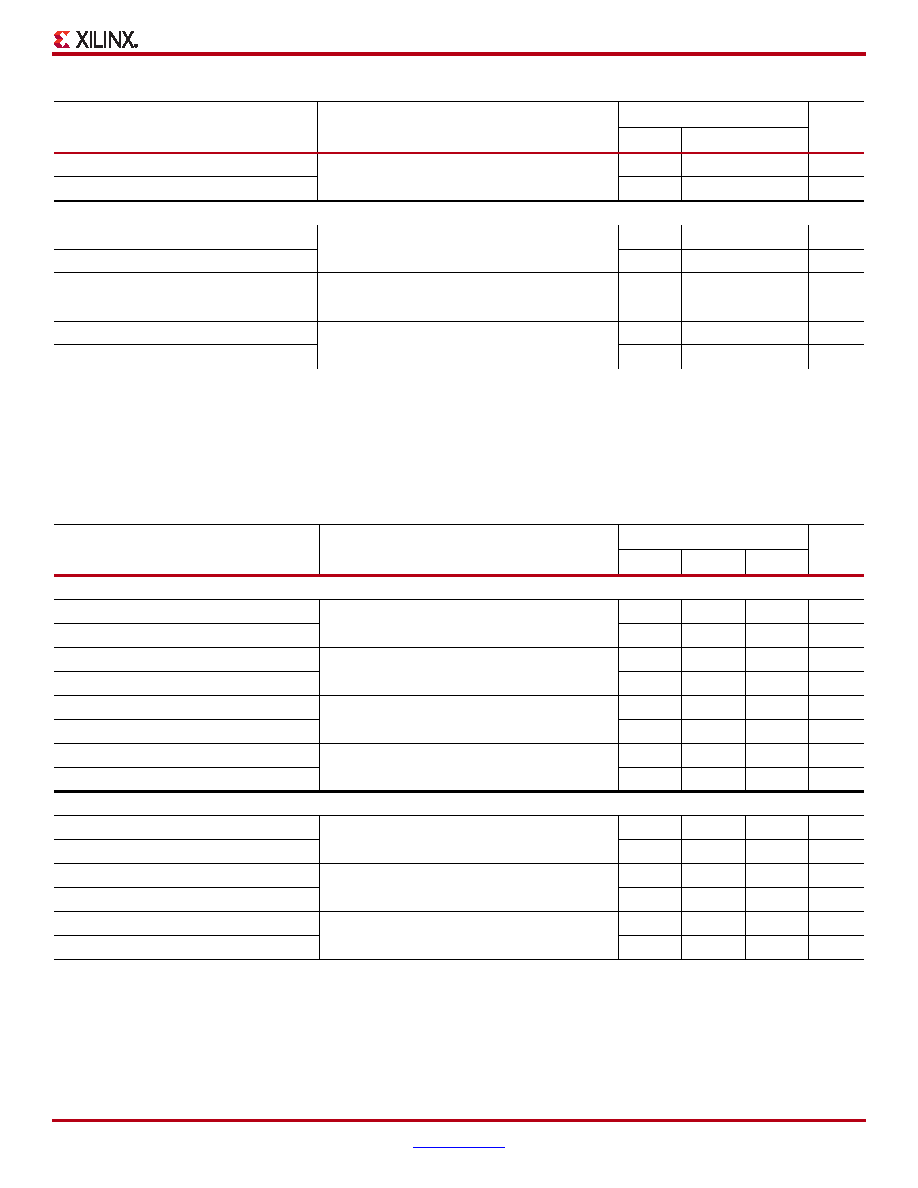

Table 45: Operating Frequency Ranges for DCM in Maximum Speed (MS) Mode (Continued)

Symbol

Description

Speed Grade

Units

-12

-11

-10

Table 46: Operating Frequency Ranges for DCM in Maximum Range (MR) Mode

Symbol

Description

Speed Grade

Units

-12

-11

-10

Outputs Clocks (Low Frequency Mode)

CLKOUT_FREQ_1X_LF_MR_MIN

CLK0, CLK90, CLK180, CLK270

19

MHz

CLKOUT_FREQ_1X_LF_MR_MAX

40

36

32

MHz

CLKOUT_FREQ_2X_LF_MR_MIN

CLK2X, CLK2X180

38

MHz

CLKOUT_FREQ_2X_LF_MR_MAX

80

72

64

MHz

CLKOUT_FREQ_DV_LF_MR_MIN

CLKDV

1.2

MHz

CLKOUT_FREQ_DV_LF_MR_MAX

26.7

24

21.3

MHz

CLKOUT_FREQ_FX_LF_MR_MIN

CLKFX, CLKFX180

19

MHz

CLKOUT_FREQ_FX_LF_MR_MAX

40

36

32

MHz

Input Clocks (Low Frequency Mode)

CLKIN_FREQ_DLL_LF_MR_MIN

CLKIN (using DLL outputs)(1,3,4,5,6)

19

MHz

CLKIN_FREQ_DLL_LF_MR_MAX

40

36

32

MHz

CLKIN_FREQ_FX_LF_MR_MIN

CLKIN (using DFS outputs only)(2,3,4)

111

MHz

CLKIN_FREQ_FX_LF_MR_MAX

35

32

28

MHz

PSCLK_FREQ_LF_MR_MIN

PSCLK

111

KHz

PSCLK_FREQ_LF_MR_MAX

262.50

236.30

210.00

MHz

Notes:

1.

DLL Outputs are used in these instances to describe the outputs: CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180, and CLKDV.

2.

DFS Outputs are used in these instances to describe the outputs: CLKFX and CLKFX180.

3.

When using the DCMs CLKIN_DIVIDE_BY_2 attribute these values should be doubled.

4.

When using a CLKIN frequency > 400 MHz and the DCMs CLKIN_DIVIDE_BY_2 attribute, the CLKIN duty cycle must be within ±5% (45/55 to

55/45).

5.

The DCM must be reset if the clock input clock stops for more than 100 ms.

6.

These values also apply when using both DLL and DFS outputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4VFX100-11FFG1152I | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-11FFG1517I | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

| XC4VFX100-12FFG1152C | FPGA, 10544 CLBS, 1181 MHz, PBGA1152 |

| XC4VFX100-12FFG1517C | FPGA, 10544 CLBS, 1181 MHz, PBGA1517 |

| XC5206-3PCG84I | FPGA, 196 CLBS, 6000 GATES, 83 MHz, PQCC84 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4VFX100-11FF1152C | 制造商:Xilinx 功能描述:FPGA VIRTEX-4 94896 CELLS 90NM 1.2V 1152FCBGA - Trays |

| XC4VFX100-11FF1152CES1 | 制造商:Xilinx 功能描述: |

| XC4VFX100-11FF1152CES4 | 制造商:Xilinx 功能描述: |

| XC4VFX100-11FF1152CES4S | 制造商:Xilinx 功能描述: |

| XC4VFX100-11FF1152I | 功能描述:IC FPGA VIRTEX-4FX 1517FFBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Virtex®-4 FX 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。