- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4245 > XC2S600E-6FGG456C (Xilinx Inc)IC SPARTAN-IIE FPGA 600K 456FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S600E-6FGG456C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 73/108頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 600K 456FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 3456 |

| 邏輯元件/單元數(shù): | 15552 |

| RAM 位總計(jì): | 294912 |

| 輸入/輸出數(shù): | 329 |

| 門數(shù): | 600000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 456-BBGA |

| 供應(yīng)商設(shè)備封裝: | 456-FBGA |

| 其它名稱: | 122-1332 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當(dāng)前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

DS077-4 (v3.0) August 9, 2013

67

Product Specification

Spartan-IIE FPGA Family: Pinout Tables

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

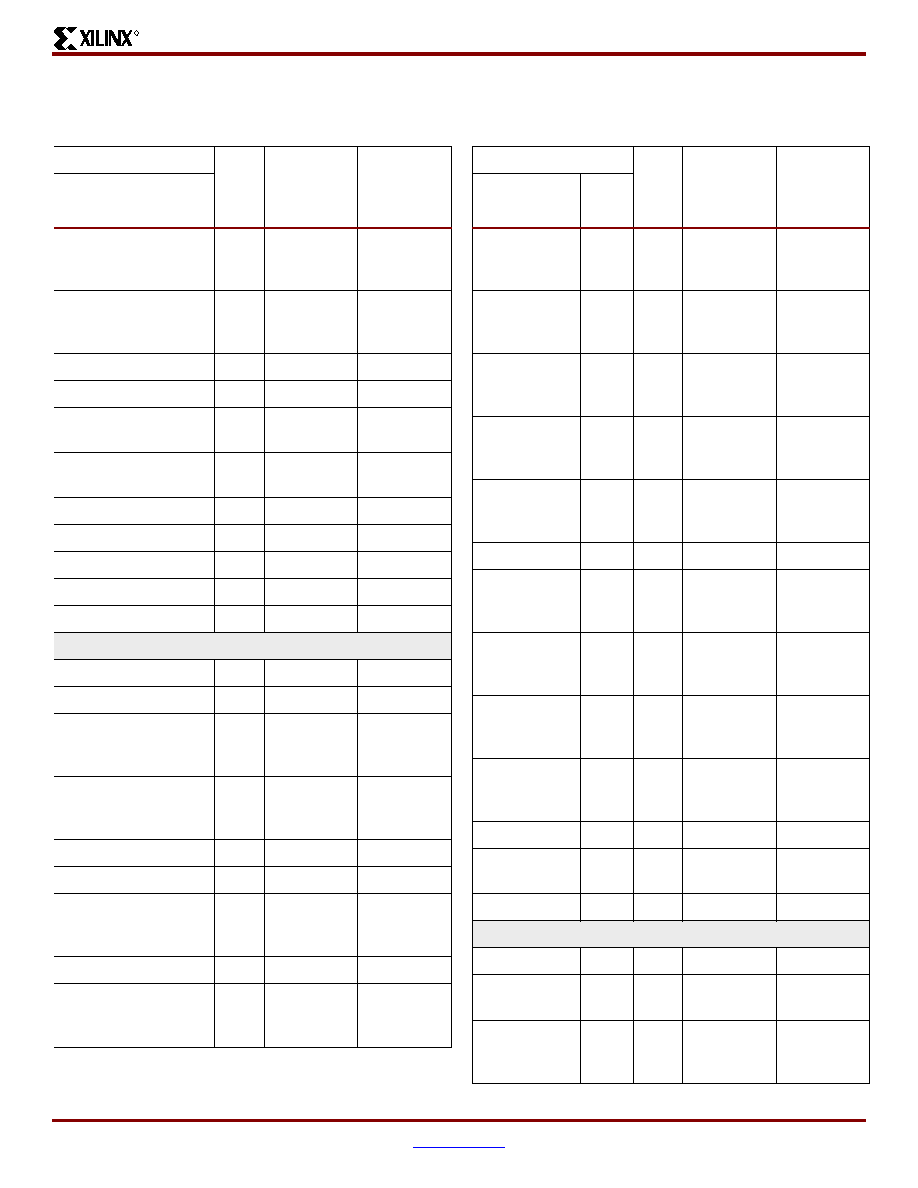

I/O, L65P

6

L4

XC2S50E,

150E, 200E,

300E, 400E

-

I/O, VREF

Bank 6, L65N

6

L5

XC2S50E,

150E, 200E,

300E, 400E

All

I/O, L64P_YY

6

M3

All

-

I/O, L64N_YY

6

M4

All

-

I/O, L63P

6

N2

XC2S100E,

200E, 300E

-

I/O, L63N

6

N3

XC2S100E,

200E, 300E

XC2S200E,

300E, 400E

I/O, L62P_YY

6

P1

All

-

I/O, L62N_YY

6

P2

All

-

M1

-

R1

-

M0

-

T2

-

M2

-

R3

-

I/O, L61N_YY

5

P4

All

-

I/O, L61P_YY

5

R4

All

-

I/O, L60N

5

T3

XC2S50E,

100E, 200E,

300E, 400E

XC2S200E,

300E, 400E

I/O, L60P

5

T4

XC2S50E,

100E, 200E,

300E, 400E

-

I/O, L59N_YY

5

N5

All

-

I/O, L59P_YY

5

P5

All

-

I/O, VREF

Bank 5,

L58N_YY

5

R5

All

I/O, L58P_YY

5

T5

All

-

I/O, L57N

5

N6

XC2S50E,

100E, 150E,

300E

-

FT256 Pinouts (XC2S50E, XC2S100E,

XC2S150E, XC2S200E, XC2S300E, XC2S400E)

(Continued)

Pad Name

Pin

LVDS

Async.

Output

Option

VREF

Option

Function

Bank

I/O, L57P

5

P6

XC2S50E,

100E, 150E,

300E

-

I/O, L56N

5

R6

XC2S50E,

100E, 200E,

300E, 400E

XC2S100E,

150E, 200E,

300E, 400E

I/O, L56P

5

T6

XC2S50E,

100E, 200E,

300E, 400E

-

I/O, L55N

5

M6

XC2S50E,

100E, 200E,

300E, 400E

-

I/O, L55P

5

N7

XC2S50E,

100E, 200E,

300E, 400E

-

I/O

5

P7

-

I/O, L54N

5

R7

XC2S50E,

200E, 300E,

400E

-

I/O, L54P

5

T7

XC2S50E,

200E, 300E,

400E

-

I/O, VREF

Bank 5, L53N

5

M7

XC2S50E,

200E, 300E,

400E

All

I/O, L53P

5

N8

XC2S50E,

200E, 300E,

400E

-

I/O

5

P8

-

XC2S400E

I/O (DLL),

L52N

5

R8

-

GCK1, I

5

T8

-

GCK0, I

4

T9

-

I/O (DLL),

L52P

4

R9

-

I/O, L51N

4

P9

XC2S50E,

150E, 200E,

400E

XC2S400E

FT256 Pinouts (XC2S50E, XC2S100E,

XC2S150E, XC2S200E, XC2S300E, XC2S400E)

(Continued)

Pad Name

Pin

LVDS

Async.

Output

Option

VREF

Option

Function

Bank

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 25LC128T-E/ST | IC EEPROM 128KBIT 10MHZ 8TSSOP |

| XCV100E-7BG352I | IC FPGA 1.8V I-TEMP 352-MBGA |

| 25LC128XT-E/ST | IC EEPROM 128KBIT 10MHZ 8TSSOP |

| 3342-4 | JACK SCREW KIT, .35" LENGTH |

| 3342-1 | JACK SCREW KIT, .22" LENGTH |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S600E-6FGG456I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-6FGG676C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-6FGG676C4022 | 制造商:Xilinx 功能描述: |

| XC2S600E-6FGG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-6FT256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。