- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19498 > XC2C64A-7CPG56C (Xilinx Inc)IC CR-II CPLD 64MCELL 56-BGA PDF資料下載

參數(shù)資料

| 型號: | XC2C64A-7CPG56C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 2/16頁 |

| 文件大小: | 0K |

| 描述: | IC CR-II CPLD 64MCELL 56-BGA |

| 標準包裝: | 360 |

| 系列: | CoolRunner II |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 最大延遲時間 tpd(1): | 6.7ns |

| 電壓電源 - 內(nèi)部: | 1.7 V ~ 1.9 V |

| 邏輯元件/邏輯塊數(shù)目: | 4 |

| 宏單元數(shù): | 64 |

| 門數(shù): | 1500 |

| 輸入/輸出數(shù): | 45 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 56-LFBGA,CSPBGA |

| 供應(yīng)商設(shè)備封裝: | 56-CSBGA(6x6) |

| 包裝: | 托盤 |

| 產(chǎn)品目錄頁面: | 600 (CN2011-ZH PDF) |

| 配用: | 122-1536-ND - KIT STARTER SPARTAN-3E 122-1532-ND - KIT DEVELOPMENT SPARTAN 3ADSP |

| 其它名稱: | 122-1408 |

CoolRunner-II CPLD Family

10

DS090 (v3.1) September 11, 2008

Product Specification

R

Design Security

Designs can be secured during programming to prevent

either accidental overwriting or pattern theft via readback.

Four independent levels of security are provided on-chip,

eliminating any electrical or visual detection of configuration

patterns. These security bits can be reset only by erasing

the entire device. See WP170 for more detail.

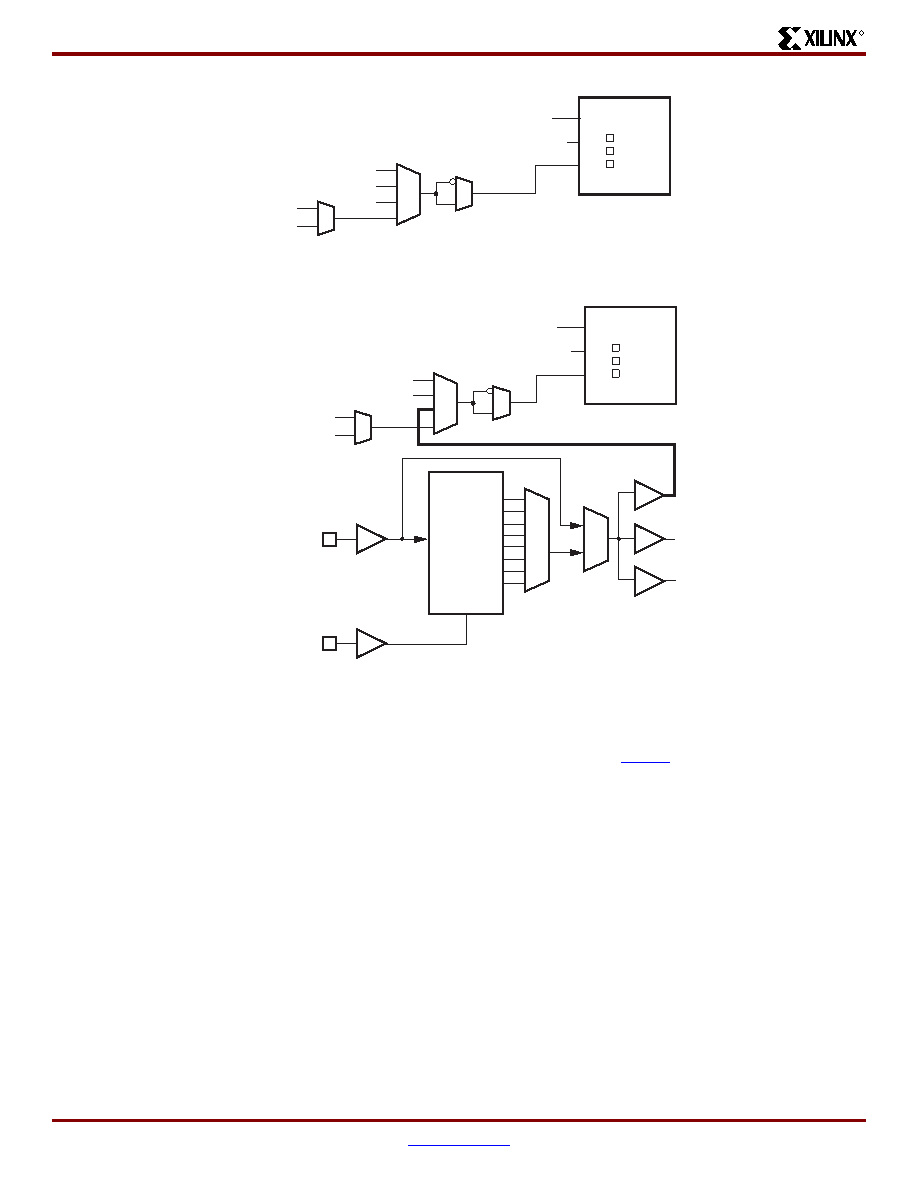

Figure 9: Macrocell Clock Chain with DualEDGE Option Shown

Figure 10: CoolCLOCK Created by Cascading Clock Divider and DualEDGE Option

GCK0

GCK1

GCK2

CLK_CT

PTC

DS090_09_121201

D/T

CE

CK

FIF

Latch

DualEDGE

Q

GCK0

GCK1

GCK2

CTC

PTC

D/T

CE

CK

FIF

Latch

DualEDGE

Q

Clock

In

÷2

÷4

÷6

÷8

÷10

÷12

÷14

÷16

GCK2

Synch Reset

Synch Rst

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ESM40DTAS | CONN EDGECARD 80POS R/A .156 SLD |

| TAP106M020CRW | CAP TANT 10UF 20V 20% RADIAL |

| VE-B0Y-CX-F3 | CONVERTER MOD DC/DC 3.3V 49.5W |

| LT3083IT#TRPBF | IC REG LDO ADJ 3A TO220-5 |

| IRU1015-33CP | IC REG LDO 3.3V 1.5A 2-UTHINPAK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2C64A-7CPG56C7013 | 制造商:Xilinx 功能描述: |

| XC2C64A-7CPG56I | 功能描述:IC CR-II CPLD 64MCELL 56-CSBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:CoolRunner II 標準包裝:90 系列:ispMACH® 4A 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時間 tpd(1):7.5ns 電壓電源 - 內(nèi)部:4.75 V ~ 5.25 V 邏輯元件/邏輯塊數(shù)目:- 宏單元數(shù):64 門數(shù):- 輸入/輸出數(shù):48 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:100-LQFP 供應(yīng)商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 |

| XC2C64A-7CPG56I4124 | 制造商:Xilinx 功能描述: |

| XC2C64A-7PC44C | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC2C64A-7PC44I | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。