- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1973 > XA3SD3400A-4FGG676I (Xilinx Inc)SPARTAN-3ADSP FPGA 3400K 676FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XA3SD3400A-4FGG676I |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 43/58頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | SPARTAN-3ADSP FPGA 3400K 676FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Extended Spartan 3A FPGA Family |

| 標(biāo)準(zhǔn)包裝: | 40 |

| 系列: | Spartan®-3A DSP XA |

| LAB/CLB數(shù): | 5968 |

| 邏輯元件/單元數(shù): | 53712 |

| RAM 位總計(jì): | 2322432 |

| 輸入/輸出數(shù): | 469 |

| 門數(shù): | 3400000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 676-BGA |

| 供應(yīng)商設(shè)備封裝: | 676-FBGA(27x27) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

XA Spartan-3A DSP Automotive FPGA Family Data Sheet

DS705 (v2.0) April 18, 2011

Product Specification

48

Configuration and JTAG Timing

General Configuration Power-On/Reconfigure Timing

X-Ref Target - Figure 11

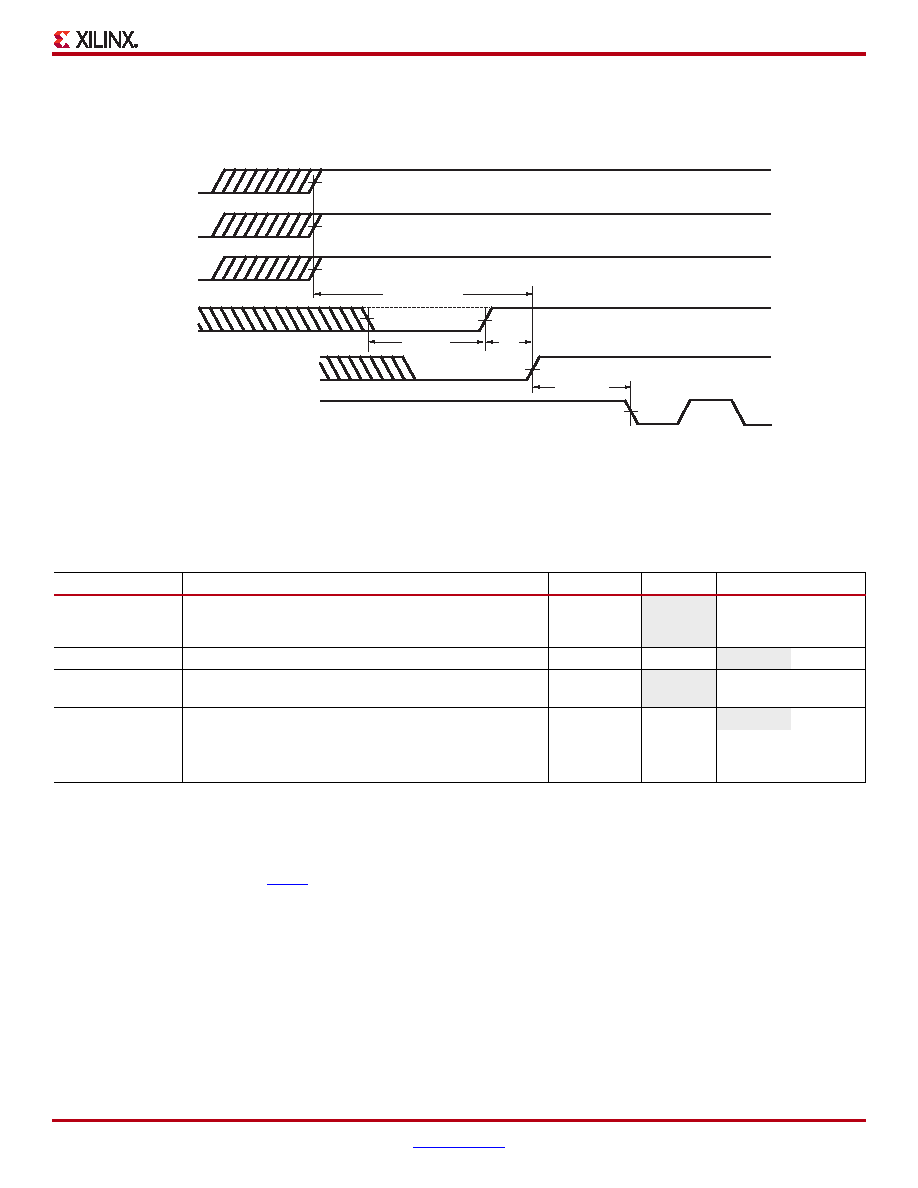

Figure 11: Waveforms for Power-On and the Beginning of Configuration

Table 46: Power-On Timing and the Beginning of Configuration

Symbol

Description

Device

Min

Max

Units

TPOR(2)

The time from the application of VCCINT, VCCAUX, and VCCO

Bank 2 supply voltage ramps (whichever occurs last) to the

rising transition of the INIT_B pin

All

–18

ms

TPROG

The width of the low-going pulse on the PROG_B pin

All

0.5

–s

TPL(2)

The time from the rising edge of the PROG_B pin to the

rising transition on the INIT_B pin

All

–2

ms

TINIT

Minimum Low pulse width on INIT_B output

All

300

–ns

TICCK(3)

The time from the rising edge of the INIT_B pin to the

generation of the configuration clock signal at the CCLK

output pin

All

0.5

4

s

Notes:

1.

The numbers in this table are based on the operating conditions set forth in Table 8. This means power must be applied to all VCCINT, VCCO,

and VCCAUX lines.

2.

Power-on reset and the clearing of configuration memory occurs during this period.

3.

This specification applies only to the SPI and BPI modes.

4.

For details on configuration, see UG332, Spartan-3 Generation Configuration User Guide.

VCCINT

(Supply)

VCCAUX

VCCO Bank 2

PROG_B

(Output)

(Open-Drain)

(Input)

INIT_B

CCLK

DS705_11_041311

1.2V

2.5V

T

ICCK

T

PROG

T

PL

T

POR

1.0V

2.0V

3.3V

or

2.5V

3.3V

or

Notes:

1.

The VCCINT, VCCAUX, and VCCO supplies can be applied in any order.

2.

The Low-going pulse on PROG_B is optional after power-on.

3.

The rising edge of INIT_B samples the voltage levels applied to the mode pins (M0 – M2).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XA6SLX75T-3FGG484Q | IC FPGA SPARTAN 6 484FGGBGA |

| XA95144XL-15CSG144I | IC CPLD 144MC 117 I/O 144CSBGA |

| XAM1808AZCE4 | IC ARM PROCESSOR 361NFBGA |

| XC1765ESOG8C | IC PROM SERIAL 65K 8-SOIC |

| XC17S200AVQ44I | IC PROM SER 200000 I-TEMP 44VQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X-A4A-300L | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4C-300M | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4M-300L | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4M-300M | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

| X-A4N | 制造商:Leach International Corporation 功能描述:MID RANGE - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。