- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄231494 > WE128K32N300H1Q (WHITE ELECTRONIC DESIGNS CORP) EEPROM 5V MODULE, CPGA66 PDF資料下載

參數(shù)資料

| 型號(hào): | WE128K32N300H1Q |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | PROM |

| 英文描述: | EEPROM 5V MODULE, CPGA66 |

| 封裝: | 1.075 X 1.075 INCH, HERMETIC SEALED, CERAMIC, HIP-66 |

| 文件頁(yè)數(shù): | 9/14頁(yè) |

| 文件大?。?/td> | 497K |

| 代理商: | WE128K32N300H1Q |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

4

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

White Electronic Designs

WE128K32-XXX

March 2008

Rev. 12

White Electronic Designs Corp. reserves the right to change products or specications without notice.

WRITE

A write cycle is initiated when OE# is high and a low pulse

is on WE# or CS# with CS# or WE# low. The address

is latched on the falling edge of CS# or WE# whichever

occurs last. The data is latched by the rising edge of CS#

or WE#, whichever occurs rst. A byte write operation will

automatically continue to completion.

write cycle timing

Figures 5 and 6 show the write cycle timing relationships.

A write cycle begins with address application, write enable

and chip select. Chip select is accomplished by placing

the CS# line low. Write enable consists of setting the WE#

line low. The write cycle begins when the last of either CS#

or WE# goes low.

The WE# line transition from high to low also initiates

an internal 150 μsec delay timer to permit page mode

operation. Each subsequent WE# transition from high to

low that occurs before the completion of the 150 μsec time

out will restart the timer from zero. The operation of the

timer is the same as a retriggerable one-shot.

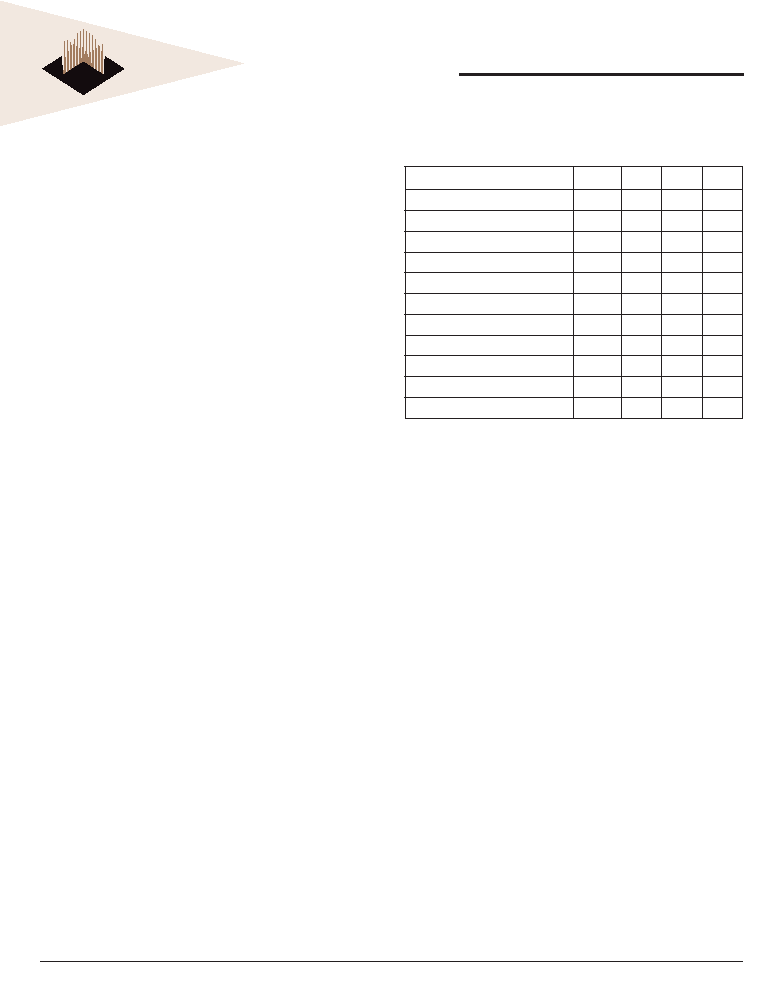

AC WRITE CHARACTERISTICS

VCC = 5.0V, GND = 0V, -55°C ≤ TA ≤ +125°C

Write Cycle Parameter

Symbol

Min

Max

Unit

Write Cycle Time, TYP = 6ms

tWC

10

ms

Address Set-up Time

tAS

0ns

Write Pulse Width (WE# or CS#)

tWP

100

ns

Chip Select Set-up Time

tCS

0ns

Address Hold Time

tAH

100

ns

Data Hold Time

tDH

10

ns

Chip Select Hold Time

tCSH

0ns

Data Set-up Time

tDS

50

ns

Output Enable Set-up Time

tOES

0ns

Output Enable Hold Time

tOEH

0ns

Write Pulse Width High

tWPH

50

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WE128K32P125G2TC | EEPROM 5V MODULE, CQFP68 |

| W3DG6418V10D2IMG | 16M X 64 SYNCHRONOUS DRAM MODULE, DMA168 |

| W3DG6418V10D2SG | 16M X 64 SYNCHRONOUS DRAM MODULE, DMA168 |

| W3EG2128M72AFSR265AD3MG | 256M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG72128S202D3S | 128M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| WE128K32N-300H1Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 EEPROM Module |

| WE128K32N-300H1QA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 EEPROM Module |

| WE128K32N-300HI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 EEPROM Module |

| WE128K32N-300HM | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 EEPROM Module |

| WE128K32N-300HQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 EEPROM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。