- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄231491 > W3EG72256S202AJD3S (MICROSEMI CORP-PMG MICROELECTRONICS) 256M X 72 DDR DRAM MODULE, 0.8 ns, DMA184 PDF資料下載

參數(shù)資料

| 型號(hào): | W3EG72256S202AJD3S |

| 廠商: | MICROSEMI CORP-PMG MICROELECTRONICS |

| 元件分類: | DRAM |

| 英文描述: | 256M X 72 DDR DRAM MODULE, 0.8 ns, DMA184 |

| 封裝: | DIMM-184 |

| 文件頁數(shù): | 11/14頁 |

| 文件大小: | 307K |

| 代理商: | W3EG72256S202AJD3S |

White Electronic Designs

W3EG72256S-JD3

-AJD3

6

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

December 2004

Rev. 2

PRELIMINARY

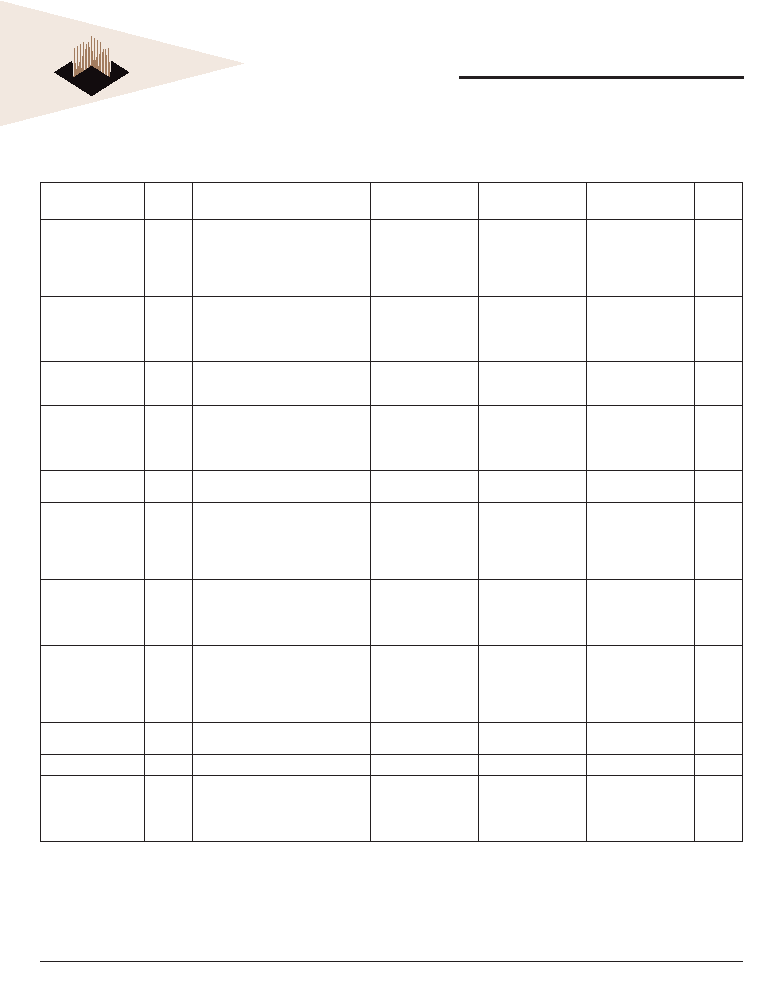

IDD SPECIFICATIONS AND TEST CONDITIONS

0°C

≤ TA ≤ 70°C, VCCQ = 2.5V ± 0.2V, VCC = 2.5V ± 0.2V

Includes PLL and register power

Parameter

Symbol

Conditions

DDR333@CL=2.5*

Max

DDR266@CL=2, 2.5

Max

DDR200@CL=2

Max

Units

Operating Current

IDD0

One device bank; Active - Precharge;

tRC=tRC (MIN); tCK=tCK (MIN); DQ,DM

and DQS inputs changing once per

clock cycle; Address and control

inputs changing once every two

cycles.

3155

2885

mA

Operating Current

IDD1

One device bank; Active-Read-

Precharge Burst = 2; tRC=tRC (MIN);

tCK=tCK (MIN); lOUT = 0mA; Address

and control inputs changing once per

clock cycle.

3785

3515

mA

Precharge Power-

Down Standby

Current

IDD2P

All device banks idle; Power-down

mode; tCK=tCK (MIN); CKE=(low)

180

rnA

Idle Standby Current

IDD2F

CS# = High; All device banks idle;

tCK=tCK (MIN); CKE = high; Address

and other control inputs changing

once per clock cycle. VIN = VREF for

DQ, DQS and DM.

1480

1390

mA

Active Power-Down

Standby Current

IDD3P

One device bank active; Power-Down

mode; tCK (MIN); CKE=(low)

630

540

mA

Active Standby

Current

IDD3N

CS# = High; CKE = High; One device

bank; Active-Precharge; tRC=tRAS

(MAX); tCK=tCK (MIN); DQ, DM and

DQS inputs changing twice per clock

cycle; Address and other control

inputs changing once per clock cycle.

1210

1120

mA

Operating Current

IDD4R

Burst = 2; Reads; Continuous burst;

One device bank active; Address

and control inputs changing once

per clock cycle; TCK= TCK (MIN); lOUT

= 0mA.

4235

3875

mA

Operating Current

IDD4W

Burst = 2; Writes; Continuous burst;

One device bank active; Address

and control inputs changing once per

clock cycle; tCK=tCK (MIN); DQ,DM

and DQS inputs changing once per

clock cycle.

4415

4055

rnA

Auto Refresh

Current

IDD5

tRC = tRC (MIN)

6430

6250

mA

Self Refresh Current

IDD6

CKE

≤ 0.2V

472

mA

Operating Current

IDD7A

Four bank interleaving Reads (BL=4)

with auto precharge with tRC=tRC

(MIN); tCK=tCK (MIN); Address and

control inputs change only during

Active Read or Write commands.

9725

9005

mA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W3EG72256S262JD3MF | 256M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3EG7232S335AD4ISG | 32M X 72 DDR DRAM MODULE, 0.7 ns, DMA200 |

| W3EG7266S262D3S | 64M X 72 DDR DRAM MODULE, 0.75 ns, DMA184 |

| W3HG264M72EER403AD7S | 128M X 72 DDR DRAM MODULE, 0.6 ns, DMA244 |

| W7NCF01GH10IS4BG | 64M X 16 FLASH 3.3V PROM CARD, 150 ns, UUC50 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3EG72256S202JD3 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2GB-256Mx72 DDR SDRAM REGISTERED ECC w/PLL |

| W3EG72256S262AJD3 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2GB-256Mx72 DDR SDRAM REGISTERED ECC w/PLL |

| W3EG72256S262JD3 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2GB-256Mx72 DDR SDRAM REGISTERED ECC w/PLL |

| W3EG72256S263AJD3 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2GB-256Mx72 DDR SDRAM REGISTERED ECC w/PLL |

| W3EG72256S263JD3 | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2GB-256Mx72 DDR SDRAM REGISTERED ECC w/PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。