- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382708 > U632H64DC35 NVRAM (EEPROM Based) PDF資料下載

參數(shù)資料

| 型號: | U632H64DC35 |

| 英文描述: | NVRAM (EEPROM Based) |

| 中文描述: | NVRAM中(EEPROM的基礎(chǔ)) |

| 文件頁數(shù): | 7/14頁 |

| 文件大小: | 155K |

| 代理商: | U632H64DC35 |

7

November 01, 2001

U632H64

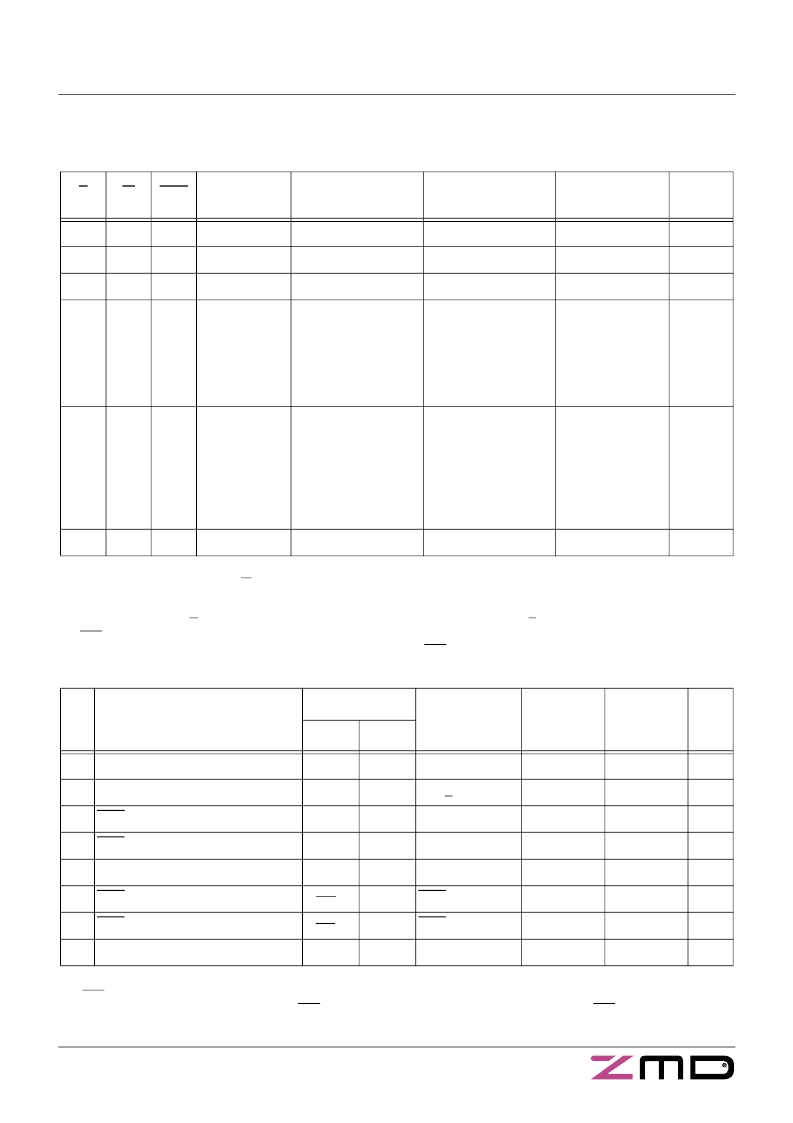

Nonvolatile Memory Operations

Mode Selection

E

W

HSB

A12 - A0

(hex)

Mode

I/O

Power

Notes

H

X

H

X

Not Selected

Output High Z

Standby

L

H

H

X

Read SRAM

Output Data

Active

l

L

L

H

X

Write SRAM

Input Data

Active

L

H

H

0000

1555

0AAA

1FFF

10F0

0F0F

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Nonvolatile STORE

Output Data

Output Data

Output Data

Output Data

Output Data

Output High Z

Active

k, l

k, l

k, l

k, l

k, l

k

L

H

H

0000

1555

0AAA

1FFF

10F0

0F0E

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Read SRAM

Nonvolatile

RECALL

Output Data

Output Data

Output Data

Output Data

Output Data

Output High Z

Active

k, l

k, l

k, l

k, l

k, l

k

X

X

L

X

STORE/Inhibit

Output High Z

I

CC2

/Standby

m

k:

The six consecutive addresses must be in order listed (0000, 1555, 0AAA, 1FFF, 10F0, 0F0F) for a Store cycle or (0000, 1555, 0AAA, 1FFF,

10F0, 0F0E) for a RECALL cycle. W must be high during all six consecutive cycles. See STORE cycle and RECALL cycle tables and dia-

grams for further details.

The following six-address sequence is used for testing purposes and should not be used: 0000, 1555, 0AAA, 1FFF, 10F0, 139C.

I/O state assumes that G

≤

V

IL

. Activation of nonvolatile cycles does not depend on the state of G.

m: HSB initiated STORE operation actually occurs only if a WRITE has been done since last STORE operation. After the STORE (if any)

completes, the part will go into standby mode inhibiting all operation until HSB rises.

l:

No.

PowerStore

Power Up RECALL/

Hardware Controlled STORE

Symbol

Conditions

Min.

Max.

Unit

Alt.

IEC

24

Power Up RECALL Duration

n, e

t

RESTORE

650

μ

s

25

STORE Cycle Duration

t

HLQX

t

d(H)S

V

CC

> 4.5 V

10

ms

26

HSB Low to Inhibit On

e

t

HLQZ

t

dis(H)S

1

μ

s

27

HSB High to Inhibit Off

e

t

HHQX

t

en(H)S

700

ns

28

External STORE Pulse Width

e

t

HLHX

t

w(H)S

250

ns

HSB Output Low Current

e, o

I

HSBOL

HSB = V

OL

3

mA

HSB Output High Current

e, o

I

HSBOH

HSB = V

IL

5

60

μ

A

Low Voltage Trigger Level

V

SWITCH

4.0

4.5

V

n:

o:

t

RESTORE

starts from the time V

CC

rises above V

SWITCH

.

HSB is an I/O that has a week internal pullup; it is basically an open drain output. It is meant to allow up to 32 U632H64 to be ganged

together for simultaneous storing. Do not use HSB to pullup any external circuitry other than other U632H64 HSB pins.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| U632H64DC45 | NVRAM (EEPROM Based) |

| U632H64DK25 | NVRAM (EEPROM Based) |

| U632H64DK35 | NVRAM (EEPROM Based) |

| U632H64DK45 | NVRAM (EEPROM Based) |

| U632H64SC25 | NVRAM (EEPROM Based) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| U632H64DC45 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NVRAM (EEPROM Based) |

| U632H64DK25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NVRAM (EEPROM Based) |

| U632H64DK35 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NVRAM (EEPROM Based) |

| U632H64DK45 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NVRAM (EEPROM Based) |

| U632H64S2C25G1 | 制造商:SIMTEK 制造商全稱:Simtek Corporation 功能描述:PowerStore 8K x 8 nvSRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。