- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98306 > TVP5151ZQCR (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PBGA48 PDF資料下載

參數(shù)資料

| 型號(hào): | TVP5151ZQCR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類(lèi): | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PBGA48 |

| 封裝: | GREEN, PLASTIC, BGA-48 |

| 文件頁(yè)數(shù): | 14/85頁(yè) |

| 文件大小: | 958K |

| 代理商: | TVP5151ZQCR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)

5

XTAL1/OSC

27.000-MHz

Crystal

CL1

CL2

XTAL2

6

R

TVP5151

CLK_IN

NC

26

IO_DVDD

10

5

XTAL1/OSC

XTAL2

6

TVP5151

CLK_IN

NC

26

IO_DVDD

10

1.8 V to 3.3 V

27.000-MHz

1.8-V Clock

5

XTAL1/OSC

XTAL2

6

TVP5151

CLK_IN

26

IO_DVDD

10

27.000-MHz

1.8-V to 3.3-V

Clock

NC

1.8 V to 3.3 V

TVP5151

www.ti.com

SLES241D – SEPTEMBER 2009 – REVISED MARCH 2011

3.15.2.3 I2C Timing Requirements

The TVP5151 decoder requires delays in the I2C accesses to accommodate its internal processor's timing.

In accordance with I2C specifications, the TVP5151 decoder holds the I2C clock line (SCL) low to indicate

the wait period to the I2C master. If the I2C master is not designed to check for the I2C clock line held-low

condition, then the maximum delays must always be inserted where required. These delays are of variable

length; maximum delays are indicated in the following diagram:

Normal register writing addresses 00h to 8Fh (addresses 90h to FFh do not require delays).

Slave

Start

address

Ack

Subaddress

Ack

Data (XXh)

Ack

Wait 64 s

Stop

(B8h)

The 64-s delay is for all registers that do not require a reinitialization. Delays may be more for some

registers.

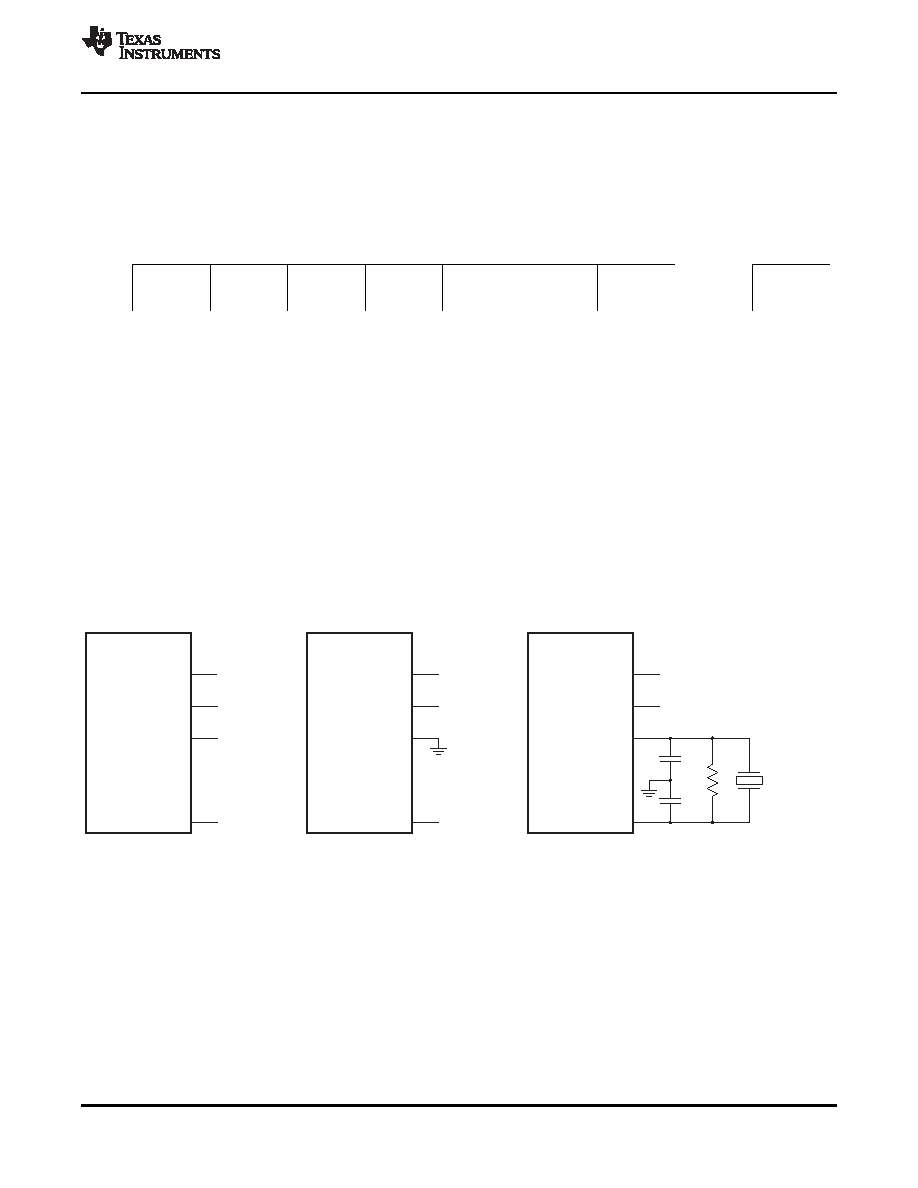

3.16 Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. A 27.000-MHz clock is required to

drive the PLL. This may be input to the TVP5151 decoder on terminal 5 (XTAL1), or a crystal of

27.000-MHz fundamental resonant frequency may be connected across terminals 5 and 6 (XTAL2).

Figure 3-8 shows the reference clock configurations. For the example crystal circuit shown (a

parallel-resonant crystal with 27.000-MHz fundamental frequency), the external capacitors must have the

following relationship:

CL1 = CL2 = 2CL – CSTRAY

where CSTRAY is the terminal capacitance with respect to ground, and CL is the crystal load capacitance

specified by the crystal manufacturer.

Figure 3-8 shows the reference clock configurations.

NOTE: The resistor (R) in parallel with the crystal is recommended to support a wide range of crystal types. A 100-k

Ω resistor

may be used for most crystal types.

Figure 3-8. Reference Clock Configurations

An alternate method to supply an external source with a 1.8-V to 3.3-V peak-to-peak level is to pull pin 5

(XTAL1/OSC) low and connect a 1.8-V to 3.3-V external oscillator clock source to pin 26, AVID/CLK_IN,

depending on what IO_DVDD supply voltage is used.

Clock source frequency should have an accuracy of ±50 ppm (max).

Copyright 2009–2011, Texas Instruments Incorporated

Functional Description

21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5151ZQC | COLOR SIGNAL DECODER, PBGA48 |

| TVP5154AIPNPR | COLOR SIGNAL DECODER, PQFP128 |

| TVP5154AIPNP | COLOR SIGNAL DECODER, PQFP128 |

| TVP5154APNPR | COLOR SIGNAL DECODER, PQFP128 |

| TVP5154APNP | COLOR SIGNAL DECODER, PQFP128 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP5154 | 制造商:Texas Instruments 功能描述:4-channel 9-bit Video Decoder TVP5154 |

| TVP5154A | 制造商:TI 制造商全稱(chēng):Texas Instruments 功能描述:4-Channel Low-Power PAL/NTSC/SECAM Video Decoder With Independent Scalers and Fast Lock |

| TVP5154AIPNP | 功能描述:視頻 IC 4Ch Lo Pwr PAL/NTSC/ SECAM Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5154AIPNPR | 功能描述:視頻 IC 4Ch Lo Pwr PAL/NTSC/ SECAM Video Decoder RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5154APNP | 功能描述:視頻 IC 4Ch Lo Pwr PAL/NTSC SECAM Vid Dec RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。