- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98301 > TSA0801IFT (STMICROELECTRONICS) 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 PDF資料下載

參數(shù)資料

| 型號(hào): | TSA0801IFT |

| 廠(chǎng)商: | STMICROELECTRONICS |

| 元件分類(lèi): | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| 封裝: | 7 X 7 MM, PLASTIC, TQFP-48 |

| 文件頁(yè)數(shù): | 6/21頁(yè) |

| 文件大小: | 0K |

| 代理商: | TSA0801IFT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

TSA0801

14/21

NO

T

FOR

NEW

DESI

G

N

Out of Range (OR)

This function is implemented on the output stage

in order to set up an "Out of Range" flag whenever

the digital data is over the full scale range.

Typically, there is a detection of all the data being

atí0í or all the data being atí1í. This ends up with

an output signal OR which is in low level state

(VOL) when the data stay within the range, or in

high level state (VOH) when the data are out of the

range.

Data Ready (DR)

The Data Ready output is an image of the clock

being synchronized on the output data (D0 to D9).

This is a very helpful signal that simplifies the syn-

chronization of the measurement equipment or

the controlling DSP.

As digital output, DR goes in high impedance state

when OEB is asserted to High level as described

in the timing diagram.

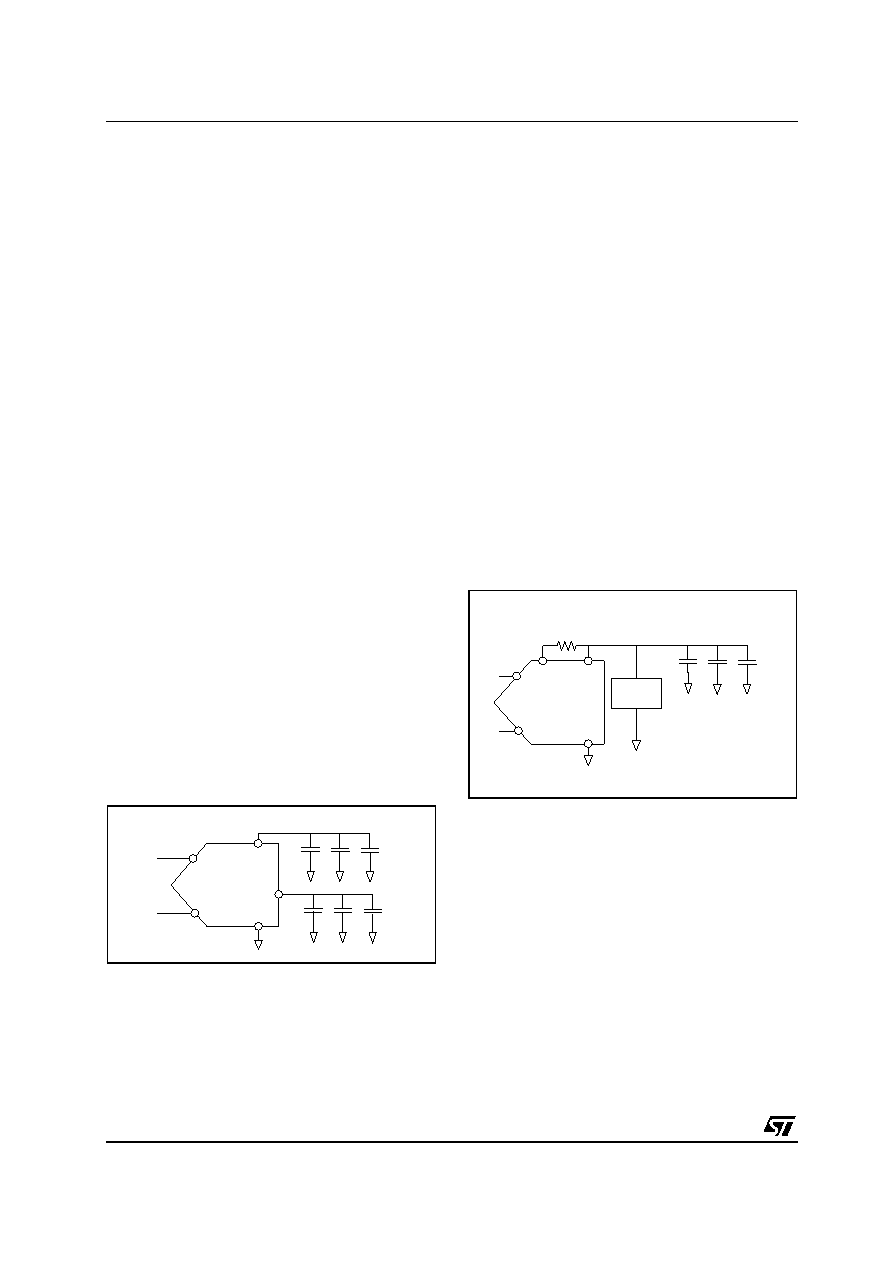

REFERENCES AND COMMON MODE

CONNECTION

VREFM must be always connected externally.

Internal reference and common mode

In the default configuration, the ADC operates with

its own reference and common mode voltages

generated by its internal bandgap. VREFM pin is

connected externally to the Analog Ground while

VREFP (respectively INCM) is set to its internal

voltage of 1.03V (respectively 0.57V). It is

recommended to decouple the VREFP in order to

minimize low and high frequency noise (refer to

Figure 1)

Figure 1 : Internal reference and common mode

setting

External reference and common mode

Each of the voltages VREFM, VREFP and INCM

can be fixed externally to better fit to the

application needs (Refer to table íOPERATING

CONDITIONSí page 2 for min/max values).

The VREFP, VREFM voltages set the analog

dynamic at the input of the converter that has a full

scale amplitude of 2*(VREFP-VREFM).

In case of analog dynamic lower than 2Vpp, the

best linearity

and

distortion

performance

is

achieved while increasing the VREFM voltage

instead of lowering the VREFP one.

The INCM is the mid voltage of the analog input

signal.

It is possible to use an external reference voltage

device for specific applications requiring even

better

linearity,

accuracy

or

enhanced

temperature behavior.

Using

the

STMicroelectronics

TS821

or

TS4041-1.2 Vref leads to optimum performances

when configured as shown on Figure 2.

Figure 2 : External reference setting

At 15Msps sampling frequency, 1MHz input

frequency

and

-1dBFS

amplitude

signal,

performances can be improved up to 2dBc on

SFDR and 0.3dB on SINAD. At 40Msps sampling

frequency, 1MHz input frequency and -1dBFS

amplitude signal, performances can be improved

up to 1dBc on SFDR and 0.6dB on SINAD.

This

can

be

very

helpful

for

example

for

multichannel application to keep a good matching

among the sampling frequency range.

TSA0801

VIN

VINB

VREFM

1.03V

VREFP

330pF

4.7uF

10nF

INCM

330pF

4.7uF

10nF

0.57V

1k

TSA0801

VIN

VINB

VREFM

VREFP

external

reference

VCCA

330pF

4.7uF

10nF

TS821

TS4041

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSA1001IF | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA1001CFT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA1001IFT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA1001CF | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| TSA1002CFT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSA1 | 制造商:HellermannTyton 功能描述:66 block bridging clip |

| TSA10 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:EURO TERMINAL BLOCKS |

| TS-A10/15L | 制造商:Stellar labs (MCM Electronics) 功能描述:Toshiba Satellite Replacement Laptop Battery |

| TSA100008-1 | 制造商:Panasonic Industrial Company 功能描述:ANTENNA |

| TSA1001 | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:10-BIT, 25MSPS, 35mW A/D CONVERTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。