- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383963 > TPS3828-xx (Texas Instruments, Inc.) PROCESSOR SUPERVISORY CIRCUITS PDF資料下載

參數(shù)資料

| 型號(hào): | TPS3828-xx |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | PROCESSOR SUPERVISORY CIRCUITS |

| 中文描述: | 處理器監(jiān)控電路 |

| 文件頁(yè)數(shù): | 6/14頁(yè) |

| 文件大小: | 217K |

| 代理商: | TPS3828-XX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

SLVS165E

–

APRIL 1998

–

REVISED DECEMBER 2002

6

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

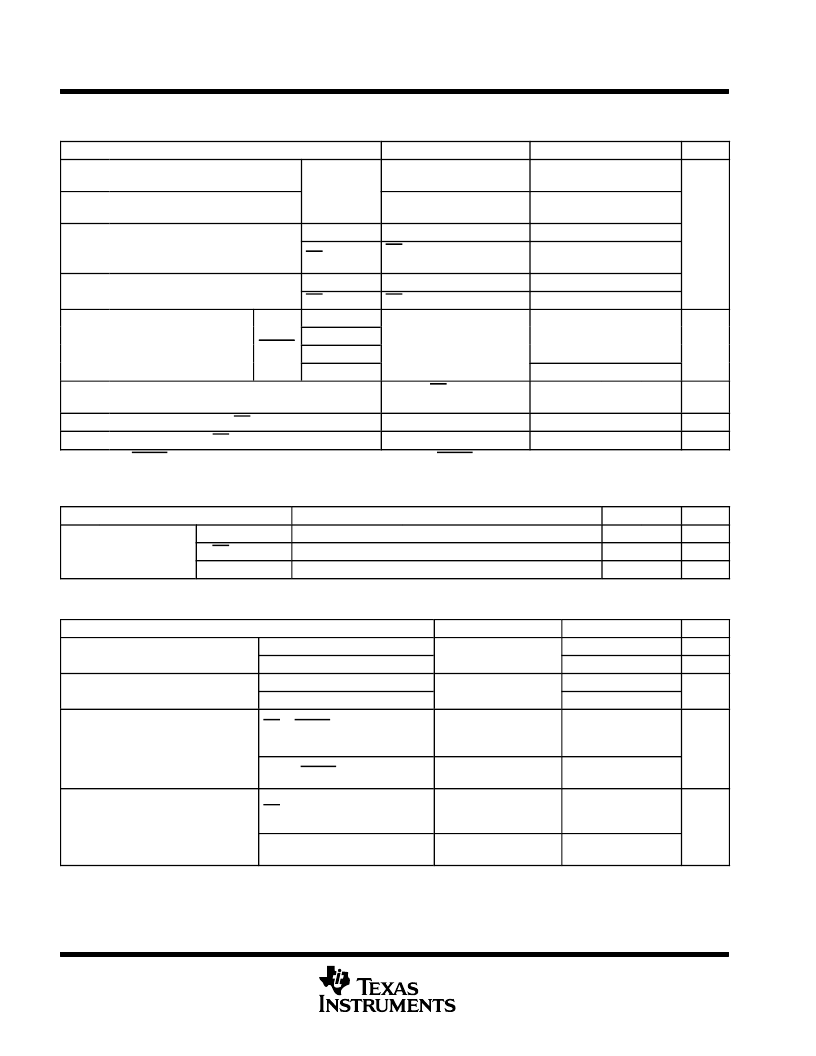

electrical characteristics over recommended operating free-air temperature range (unless

otherwise noted) (continued)

PARAMETER

TEST CONDITIONS

WDI = VDD,

time average (dc = 88%)

MIN

TYP

MAX

UNIT

IIH(AV)

Average high-level input current

WDI

120

IIL(AV)

Average low-level input current

WDI = 0.3 V, VDD = 5.5 V

time average (dc = 12%)

–

15

WDI

WDI = VDD

MR = VDD

×

0.7,

VDD = 5.5 V

WDI = 0.3 V, VDD = 5.5 V

MR = 0.3 V, VDD = 5.5 V

140

190

μ

A

IIH

High-level input current

MR

–

40

–

60

IIL

Low-level input current

le el inp t c rrent

WDI

140

190

MR

–

110

–

160

TPS382x-25

IOS

Output short-circuit current

Out ut short circuit current

(see Note 4)

RESET

TPS382x-30

VDD = VIT, max + 0.2 V,

VO = 0 V

–

400

TPS382x-33

μ

A

TPS382x-50

–

800

IDD

Supply current

WDI and MR unconnected,

Outputs unconnected

15

25

μ

A

Internal pullup resistor at MR

52

k

pF

Ci

Input capacitance at MR, WDI

NOTE 4: The RESET short-circuit current is the maximum pullup current when RESET is driven low by a

μ

P bidirectional reset pin.

VI = 0 V to 5.5 V

5

timing requirements at R

L

= 1 M

, C

L

= 50 pF, T

A

= 25

°

C

PARAMETER

TEST CONDITIONS

VDD = VIT- - 0.2 V

VIL = 0.3 x VDD,

VIL = 0.3 x VDD,

MIN

MAX

UNIT

μ

s

μ

s

ns

at VDD

at MR

at WDI

VDD = VIT

–

+ 0.2 V,

VDD

≥

VIT

–

+ 0.2 V,

VDD

≥

VIT

–

+ 0.2 V,

6

tw

Pulse width

VIH = 0.7 x VDD

VIH = 0.7 x VDD

1

100

switching characteristics at R

L

= 1 M

, C

L

= 50 pF, T

A

= 25

°

C

PARAMETER

TEST CONDITIONS

MIN

112

TYP

200

MAX

310

UNIT

ms

ttout

Watchdog time out

TPS3820

VDD

≥

VIT

–

+ 0.2 V,

See Timing Diagram

TPS3823/4/8

0.9

1.6

2.5

s

td

Dela time

Delay time

TPS3820

VDD

≥

VIT

–

+0.2 V,

See timing diagram

15

25

37

ms

TPS3823/4/5/8

120

200

300

tPHL

Propagation (delay) time,

high to low level output

high-to-low-level output

MR to RESET delay

(TPS3820/3/5/8)

VDD

≥

VIT

–

+0.2 V,

VIL=0.3 x VDD,

VIH=0.7 x VDD

VIL = VIT- - 0.2 V,

VIH = VIT- + 0.2 V

VDD

≥

VIT

–

+0.2 V,

VIL=0.3 x VDD,

VIH=0.7 x VDD

VIL = VIT- - 0.2 V,

VIH = VIT- + 0.2 V

0.1

μ

s

VDD to RESET delay

25

tPLH

Propagation (delay) time,

low to high level output

low-to-high-level output

MR to RESET delay (TPS3824/5)

0.1

μ

s

VDD to RESET delay (TPS3824/5)

25

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS3825-30DBVR | PROCESSOR SUPERVISORY CIRCUITS |

| TPS3820- | PROCESSOR SUPERVISORY CIRCUITS |

| TPS3820-25DBVT | PROCESSOR SUPERVISORY CIRCUITS |

| TPS3820-30DBVT | PROCESSOR SUPERVISORY CIRCUITS |

| TPS3820-xx | PROCESSOR SUPERVISORY CIRCUITS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS382-Q1EVM | 功能描述:EVALUATION MODULE 制造商:texas instruments 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| TPS3831A09DQNR | 制造商:Texas Instruments 功能描述:IC LP SUPERVISRY CIRCUIT 4X2SON 制造商:Texas Instruments 功能描述:SVS |

| TPS3831A09DQNT | 制造商:Texas Instruments 功能描述:IC LP SUPERVISRY CIRCUIT 4X2SON |

| TPS3831E16DQNR | 制造商:Texas Instruments 功能描述:IC LP SUPERVISRY CIRCUIT 4X2SON 制造商:Texas Instruments 功能描述:SVS |

| TPS3831E16DQNT | 制造商:Texas Instruments 功能描述: 制造商:Texas Instruments 功能描述:IC LP SUPERVISRY CIRCUIT 4X2SON |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。