- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382676 > TPS3106K33DVB (Texas Instruments, Inc.) ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS PDF資料下載

參數(shù)資料

| 型號(hào): | TPS3106K33DVB |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| 中文描述: | 超低電源電流/電源電壓監(jiān)控電路 |

| 文件頁(yè)數(shù): | 9/22頁(yè) |

| 文件大小: | 361K |

| 代理商: | TPS3106K33DVB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

SLVS363B AUGUST 2001 REVISED SEPTEMBER 2004

www.ti.com

9

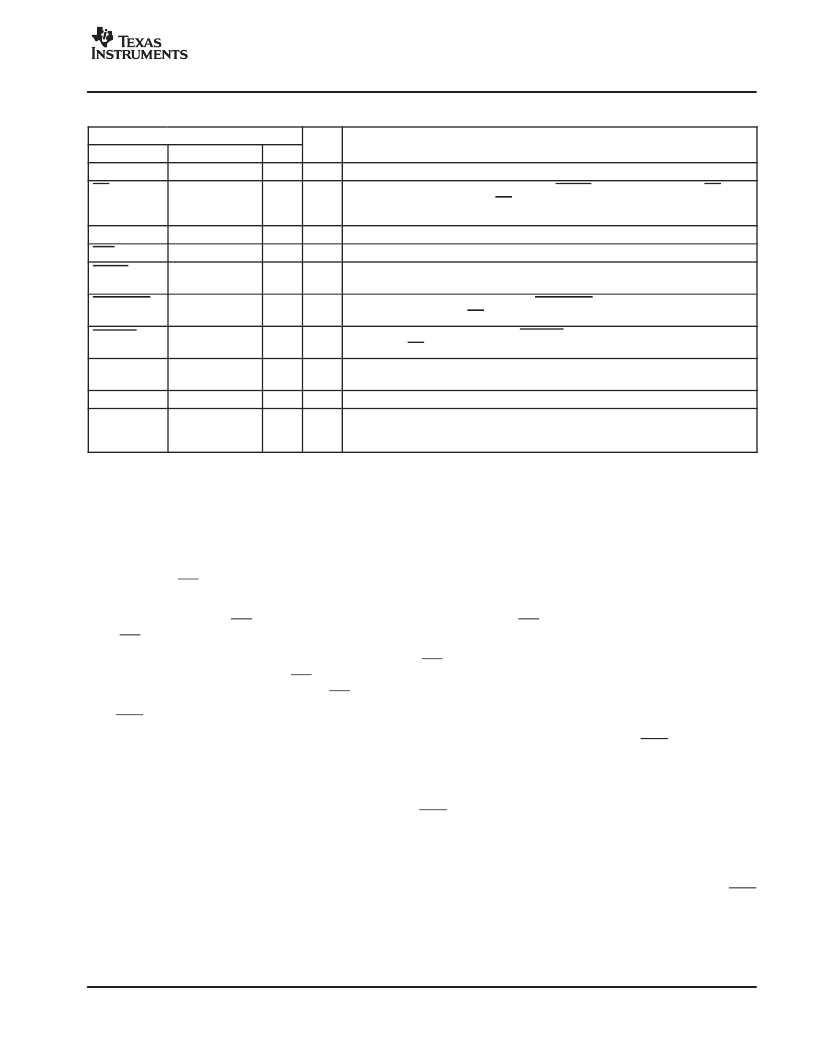

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

PART

ALL

NO.

2

GND

GND

MR

ALL

3

I

Manual-reset input. Pull low to force a reset. RESET remains low as long as MR is low

and for the timeout period after MR goes high. Leave unconnected or connect to VDD

when unused.

PFI

TPS3103

4

I

Power-fail input compares to 0.551 V with no additional delay. Connect to VDD if not used.

Power-fail output. Goes high when voltage at PFI rises above 0.551 V.

PFO

TPS3103

5

O

RESET

TPS3103

TPS3110

1

O

Active-low reset output. Either push-pull or open-drain output stage

RSTSENSE

TPS3106

5

O

Active-low reset output. Logic level at RSTSENSE only depends on the voltage at

SENSE and the status of MR.

RSTVDD

TPS3106

1

O

Active-low reset output. Logic level at RSTVDD only depends on the voltage at VDD and

the status of MR.

SENSE

TPS3106

TPS3110

4

4

I

A reset will be asserted if the voltage at SENSE is lower than 0.551 V. Connect to VDD if

unused

VDD

WDI

ALL

6

Supply voltage. Powers the device and monitors its own voltage

TPS3110

5

I

Watchdog timer input. If WDI remains high or low longer than the time-out period, then

reset is triggered. The timer clears when reset is asserted or when WDI sees a rising

edge or a falling edge.

detailed description

watchdog

The TPS3110 device integrates a watchdog timer that must be periodically triggered by a positive or negative

transition of WDI. When the supervising system fails to retrigger the watchdog circuit within the time-out interval,

RESET becomes active for the time period (t

d

). This event also reinitializes the watchdog timer.

manual reset (MR)

Many

μ

C-based products require manual-reset capability, allowing an operator or logic circuitry to initiate a

reset. Logic low at MR asserts reset. Reset remains asserted while MR is low and for a time period (t

d

) after

MR returns high. The input has an internal 100-k

pull-up resistor, so it can be left open if it is unused.

Connect a normally open momentary switch from MR to GND to create a manual reset function. External

debounce is not required. If MR is driven from long cables or if the device is used in noisy environments,

connecting a 0.1-

μ

F capacitor from MR to GND provides additional noise immunity.

PFI, PFO

The TPS3103 has an integrated power-fail (PFI) comparator with a separate open drain (PFO) output can be

used for low-battery detection, power-fail warning, or for monitoring a power supply other than the main supply.

An additional comparator is provided to monitor voltages other than the nominal supply voltage. The power-fail

input (PFI) will be compared with an internal voltage reference of 0.551 V. If the input voltage falls below the

power-fail threshold (V

IT(S)

), the power-fail output (PFO) goes low. If it goes above 0.551 V plus approximately

15-mV hysteresis, the output returns to high. By connecting two external resistors, it is possible to supervise

any voltage above 0.551 V. The sum of both resistors should be approximately 1 M

, to minimize power

consumption and to assure that the current into the PFI pin can be neglected compared with the current through

the resistor network. The tolerance of the external resistors should be not more than 1% to ensure minimal

variation of sensed voltage. If the power-fail comparator is unused, connect PFI to GND and leave PFO

unconnected. For proper operation of the PFI-comparator the supply voltage (V

DD

) must be higher than 0.8 V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS3103E09DVBR | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS3103H33DVBR | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS3103K20DVB | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS3103K20DVBR | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS3103E15DVBR | ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS3106K33DVBR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS3106K33MDBVREP | 功能描述:監(jiān)控電路 Mil Enh Ultra-Lo Spl Current/Supply Vltg RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開(kāi)關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| TPS3106XXX | 制造商:TI 制造商全稱:Texas Instruments 功能描述:UltraLow Supply-Current/Supply-Voltage Supervisory Circuits |

| TPS3110 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

| TPS311009DVB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ULTRALOW SUPPLY CURRENT/SUPPLY VOLTAGE SUPERVISORY CIRCUITS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。