- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384025 > TP3067BN (Texas Instruments, Inc.) MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER PDF資料下載

參數(shù)資料

| 型號(hào): | TP3067BN |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| 中文描述: | 整體式串行接口的PCM編解碼器和過濾器 |

| 文件頁數(shù): | 16/21頁 |

| 文件大小: | 300K |

| 代理商: | TP3067BN |

TP3064B, TP3067B, TP13064B, TP13067B

MONOLITHIC SERIAL INTERFACE

COMBINED PCMCODEC AND FILTER

SCTS031D – MAY 1990 –REVISED JULY 1996

16

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPALS OF OPERATION

asynchronous operation

For asynchronous operation, separate transmit and receive clocks can be applied. MCLKX and MCLKR must

be 2.048 MHz for the TP3064B and TP13064B, 1.536 MHz or 1.544 MHz for the TP3067B and TP13067B and

need not be synchronous. However, for best performance, MCLKR should be synchronous with MCLKX. This

is easily achieved by applying only static logic levels to MCLKR/PDN. This connects MCLKX to all internal

MCLKR functions. For 1.544-MHz operation, the device compensates for the 193rd clock pulse of each frame.

Each encoding cycle is started with FSX, and FSX must be synchronous with MCLKX and BCLKX. Each

decoding cycle is started with FSR, and FSR must be synchronous with BCLKR. The logic levels shown in

Table 1 are not valid in the asynchronous mode. BCLKX and BCLKR can operate from 64 kHz to 2.048 MHz.

short-frame sync operation

The device can operate with either a short- or a long-frame sync pulse. On power up, the device automatically

goes into the short-frame mode where both FSX and FSR must be one bit-clock period long, with timing

relationships specified in Figure 1. With FSX high during a falling edge of BCKLX, the next rising edge of BCLKX

enables the 3-state output buffer, DX, which outputs the sign bit. The remaining seven bits are clocked out on

the following seven rising edges, and the next falling edge disables DX. With FSR high during a falling edge

of BCLKR (BCLKX in synchronous mode), the next falling edge of BCLKR latches in the sign bit. The following

seven falling edges latch in the seven remaining bits. The short-frame sync pulse may be utilized in either the

synchronous or asynchronous mode.

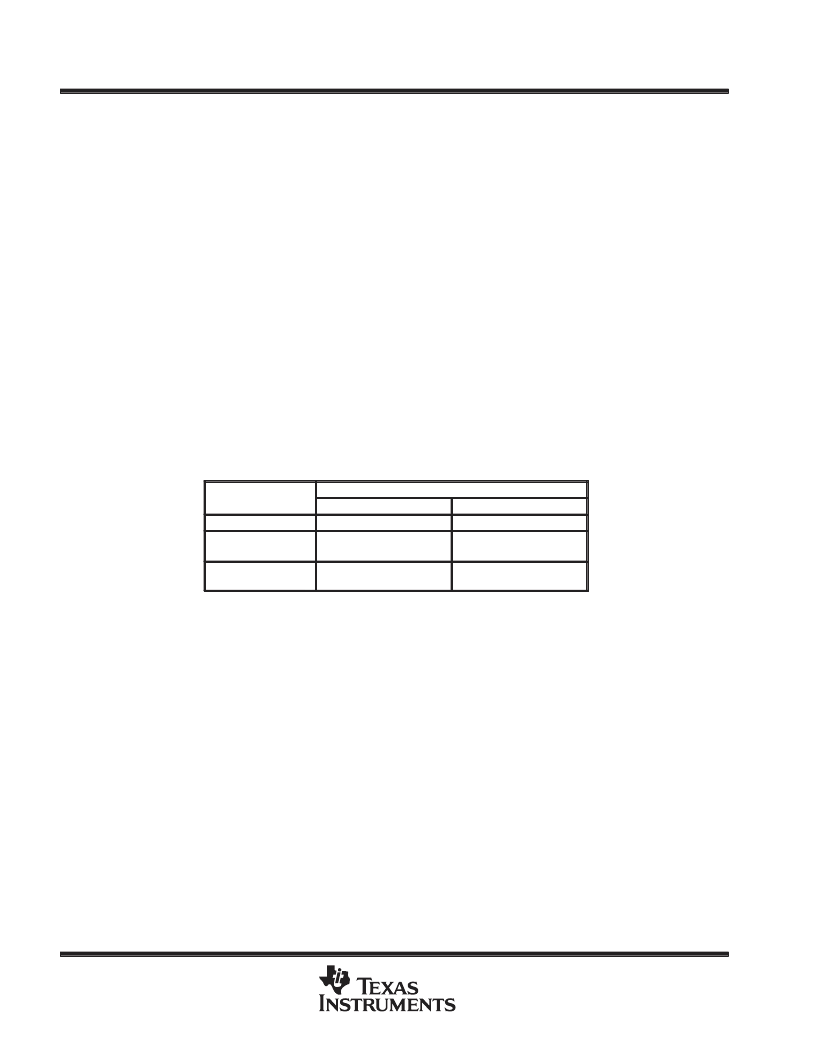

Table 1. Selection of Master-Clock Frequencies

BCLKR/CLKSEL

MASTER-CLOCK FREQUENCY SELECTED

TP3064B, TP13064B

1.536 MHz or 1.544 MHz

TP3067B, TP13067B

2.048 MHz

Clock Input

Logic Input L

(sync mode only)

Logic Input H (open)

(sync mode only)

2.048 MHz

1.536 MHz or 1.544 MHz

1.536 MHz or 1.544 MHz

2.048 MHz

long-frame sync operation

Both FSX and FSR must be three or more bit-clock periods long to use the long-frame sync mode with timing

relationships as shown in Figure 2. Using the transmit frame sync (FSX), the device detects whether a short-

or long-frame sync pulse is being used. For 64-kHz operation, the frame-sync pulse must be kept low for a

minimum of 160 ns. The rising edge of FSX or BCLKX, which ever occurs later, enables the DX 3-state output

buffer. The first bit clocked out is the sign bit. The next seven rising edges of BCLKX edges clock out the

remaining seven bits. The falling edge of BCLKX following the eighth rising edge or FSX going low, whichever

occurs later, disables DX. A rising edge on FSR, the receive frame sync pulse, causes the PCM data at DR to

be latched in on the next eight falling edges of BCLKR (BCLKX in synchronous mode). The long-frame sync

pulse can be used in either the synchronous or asynchronous mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TP13067BN | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3064B | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3064BDW | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3064BN | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3067B | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TP3067J | 制造商:Texas Instruments 功能描述: |

| TP3067N | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3067N/NOPB | 功能描述:接口—CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3067V | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:``Enhanced' Serial Interface CMOS CODEC/Filter COMBO |

| TP3067V/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:A-Law CODEC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。