- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384021 > TMS320C6455ZTZ (Texas Instruments, Inc.) Fixed-Point Digital Signal Processor PDF資料下載

參數(shù)資料

| 型號: | TMS320C6455ZTZ |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | Fixed-Point Digital Signal Processor |

| 中文描述: | 定點數(shù)字信號處理器 |

| 文件頁數(shù): | 229/250頁 |

| 文件大小: | 1838K |

| 代理商: | TMS320C6455ZTZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁當前第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁

7.20 Serial RapidIO (SRIO) Port

7.20.1 Serial RapidIO Device-Specific Information

7.20.2 Serial RapidIO Peripheral Register Description(s)

TMS320C6455

Fixed-Point Digital Signal Processor

SPRS276H–MAY 2005–REVISED OCTOBER 2007

The SRIO port on the C6455 device is a high-performance, low pin-count interconnect aimed for

embedded markets. The use of the Rapid I/O interconnect in a baseband board design can create a

homogeneous interconnect environment, providing even more connectivity and control among the

components. Rapid I/O is based on the memory and device addressing concepts of processor buses

where the transaction processing is managed completely by hardware. This enables the Rapid I/O

interconnect to lower the system cost by providing lower latency, reduced overhead of packet data

processing, and higher system bandwidth, all of which are key for wireless interfaces. The Rapid I/O

interconnect offers very low pin-count interfaces with scalable system bandwidth based on 10-Gigabit per

second (Gbps) bidirectional links.

The PHY part of the RIO consists of the physical layer and includes the input and output buffers (each

serial link consists of a differential pair), the 8-bit/10-bit encoder/decoder, the PLL clock recovery, and the

parallel-to-serial/serial-to-parallel converters.

The RapidIO interface should be designed to operate at a data rate of 3.125 Gbps per differential pair.

This equals 12.5 raw GBaud/s for the 4x RapidIO port, or approximately 9 Gbps data throughput rate.

The approach to specifying interface timing for the SRIO Port is different than on other interfaces such as

EMIF, HPI, and McBSP. For these other interfaces the device timing was specified in terms of data

manual specifications and I/O buffer information specification (IBIS) models.

For the C6455 SRIO Port, Texas Instruments (TI) provides a printed circuit board (PCB) solution showing

two DSPs connected via a 4x SRIO link directly to the user. TI has performed the simulation and system

characterization to ensure all SRIO interface timings in this solution are met. The complete SRIO system

solution is documented in the

Implementing Serial Rapid I/O PCB Layout on a TMS320C6455 Hardware

Design

application report (literature number

SPRAAA8

).

TI

only

supports designs that follow the board design guidelines outlined in the SPRAAA8

application report.

The Serial RapidIO peripheral is a master peripheral in the C6455 DSP. It conforms to the

RapidIO

Interconnect Specification, Part VI: Physical Layer 1x/4x LP-Serial Specification, Revision 1.2

.

If the SRIO peripheral is not used, the SRIO reference clock inputs and SRIO link pins can be left

unconnected. If the SRIO peripheral is enabled but not all links are used, the pins of the unused links can

be left unconnected and no terminations are needed. For more information, see the

TMS320C6455

Design Guide and Comparisons to TMS320TC6416T

(literature number

SPRAA89

).

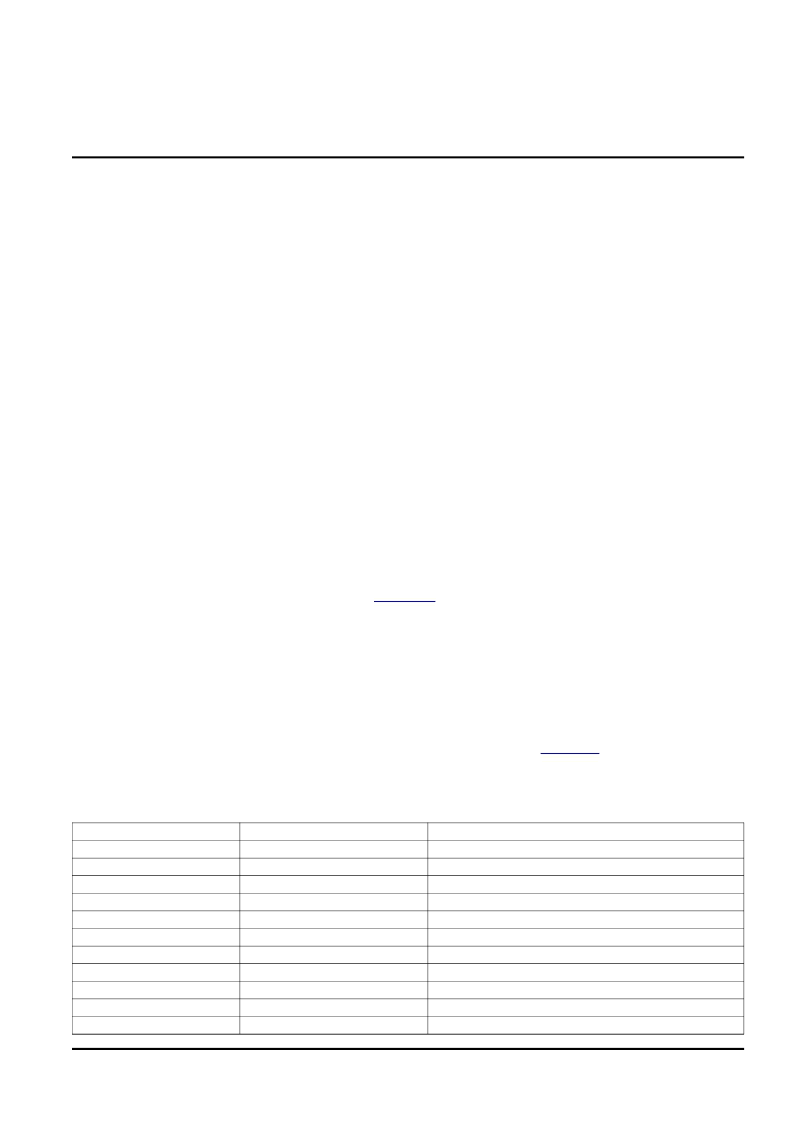

Table 7-112. RapidIO Control Registers

HEX ADDRESS RANGE

02D0 0000

02D0 0004

02D0 0008 - 02D0 001C

02D0 0020

02D0 0024 - 02D0 002C

02D0 0030

02D0 0034

02D0 0038

02D0 003C

02D0 0040

02D0 0044

ACRONYM

RIO_PID

RIO_PCR

-

RIO_PER_SET_CNTL

-

RIO_GBL_EN

RIO_GBL_EN_STAT

RIO_BLK0_EN

RIO_BLK0_EN_STAT

RIO_BLK1_EN

RIO_BLK1_EN_STAT

REGISTER NAME

Peripheral Identification Register

Peripheral Control Register

Reserved

Peripheral Settings Control Register

Reserved

Peripheral Global Enable Register

Peripheral Global Enable Status

Block Enable 0

Block Enable Status 0

Block Enable 1

Block Enable Status 1

Submit Documentation Feedback

C64x+ Peripheral Information and Electrical Specifications

229

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320C6455ZTZ7 | Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ8 | Fixed-Point Digital Signal Processor |

| TMS320C6727B_07 | Floating-Point Digital Signal Processors |

| TMS320DM355_07 | Digital Media System-on-Chip (DMSoC) |

| TMS320DM6446_07 | Digital Media System-on-Chip |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320C6455ZTZ7 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ8 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6457 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Fixed-Point Digital Signal Processor |

| TMS320C6457CCMH | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Fixed-Pt Dig Signal RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

| TMS320C6457CCMH2 | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC Fixed-Pt Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。