- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383957 > TLV320AIC23GQER (Texas Instruments, Inc.) Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier PDF資料下載

參數(shù)資料

| 型號: | TLV320AIC23GQER |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| 中文描述: | 立體聲音頻編解碼器,8到96千赫,具有集成耳機放大器 |

| 文件頁數(shù): | 24/44頁 |

| 文件大小: | 236K |

| 代理商: | TLV320AIC23GQER |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

3

–

4

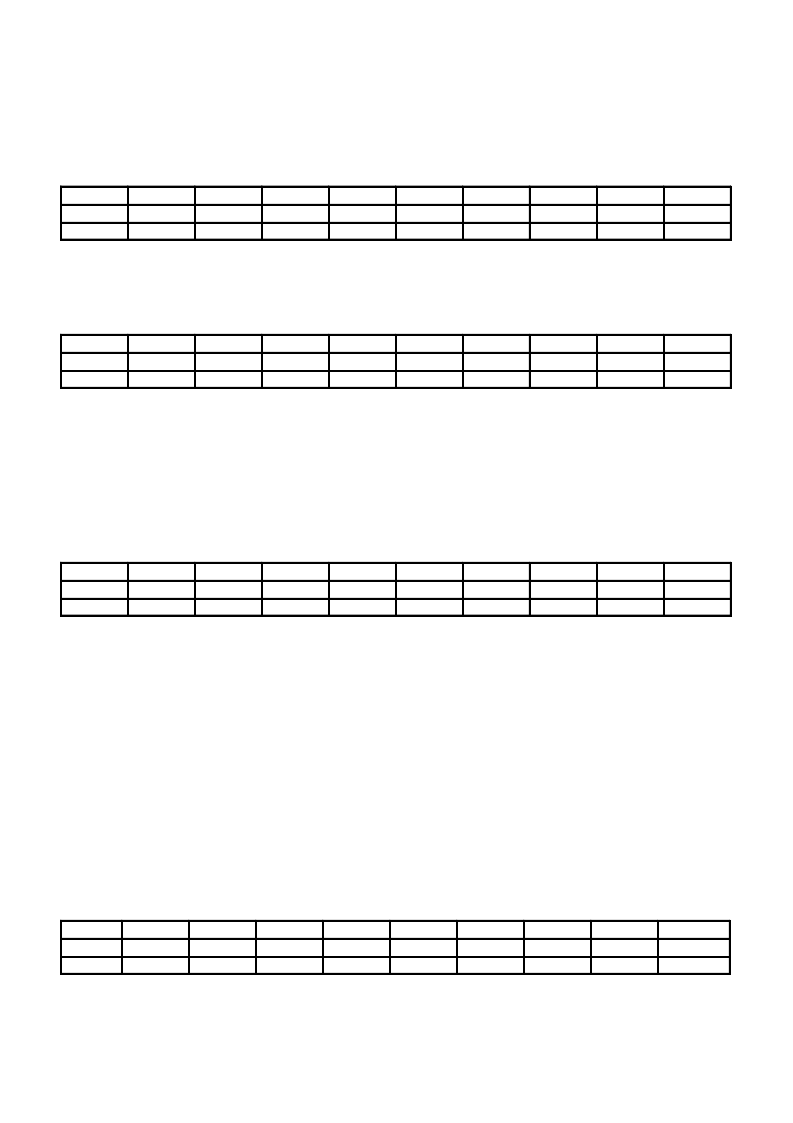

Digital Audio Path Control (Address: 0000101)

BIT

D8

D7

D6

D5

D4

D3

D2

D1

D0

Function

X

X

X

X

X

DACM

DEEMP1

DEEMP0

ADCHP

Default

0

0

0

0

0

0

1

0

0

DACM

DEEMP[1:0]

ADCHP

X

Power Down Control (Address: 0000110)

DAC soft mute

De-emphasis control

ADC high-pass filter

Reserved

0 = Disabled

00 = Disabled

0 = Disabled

1 = Enabled

01 = 32 kHz

1 = Enabled

10 = 44.1 kHz

11 = 48 kHz

BIT

D8

D7

D6

D5

D4

D3

D2

D1

D0

Function

X

OFF

CLK

OSC

OUT

DAC

ADC

MIC

LINE

Default

0

0

0

0

0

0

1

1

1

OFF

CLK

OSC

DAC

ADC

MIC

LINE

X

Digital Audio Interface Format (Address: 0000111)

Device power

Clock

Oscillator

Outputs

DAC

ADC

Microphone input

Line input

Reserved

0 = On

0 = On

0 = On

0 = On

0 = On

0 = On

0 = On

0 = On

1 = Off

1 = Off

1 = Off

1 = Off

1 = Off

1 = Off

1 = Off

1 = Off

BIT

D8

D7

D6

D5

D4

D3

D2

D1

D0

Function

X

X

MS

LRSWAP

LRP

IWL1

IWL0

FOR1

FOR0

Default

0

0

0

0

0

0

0

0

1

MS

LRSWAP

LRP

Master/slave mode

DAC left/right swap

DAC left/right phase

0 = Slave

0 = Disabled

0 = Right channel on, LRCIN high

1 = Right channel on, LRCIN low

DSP mode

1 = MSB is available on 2nd BCLK rising edge after LRCIN rising edge

0 = MSB is available on 1st BCLK rising edge after LRCIN rising edge

00 = 16 bit

01 = 20 bit

10 = 24 bit

11 = DSP format, frame sync followed by two data words

10 = I

2

S format, MSB first, left

–

1 aligned

01 = MSB first, left aligned

00 = MSB first, right aligned

1 = Master

1 = Enabled

IWL[1:0]

FOR[1:0]

Input bit length

Data format

11 = 32 bit

X

NOTES:

Reserved

1. In Master mode, the TLV320AIC23 supplies the BCLK, LRCOUT, and LRCIN. In Slave mode, BCLK, LRCOUT, and LRCIN are

supplied to the TLV320AIC23.

2. In normal mode, BCLK = MCLK/4 for all sample rates except for 88.2 kHz and 96 kHz. For 88.2 kHz and 96 kHz sample rate,

BCLK = MCLK.

3. In USB mode, bit BCLK = MCLK

Sample Rate Control (Address: 0001000)

BIT

D8

D7

D6

D5

D4

D3

D2

D1

D0

Function

X

CLKOUT

CLKIN

SR3

SR2

SR1

SR0

BOSR

USB/Normal

Default

0

0

0

1

0

0

0

0

0

CLKIN

CLKOUT

Clock input divider

Clock output divider

0 = MCLK

0 = MCLK

1 = MCLK/2

1 = MCLK/2

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC23IGQER | Stereo Audio CODEC, 8-to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC3106_0706 | LOW-POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC3106IGQE | LOW-POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV320AIC3106IGQER | LOW-POWER STEREO AUDIO CODEC FOR PORTABLE AUDIO/TELEPHONY |

| TLV341_07 | LOW-VOLTAGE RAIL-TO-RAIL OUTPUT CMOS OPERATIONAL AMPLIFLERS WITH SHUTDOWN |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AIC23IGQE | 功能描述:接口—CODEC LP Port Audio RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23IGQER | 功能描述:接口—CODEC Low-Power Portable Aud Converter RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23IPW | 功能描述:接口—CODEC LP Port Audio RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23IPWG4 | 功能描述:接口—CODEC LP Port Audio RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23IPWR | 功能描述:接口—CODEC Low-Power Portable Aud Converter RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。