- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98250 > TLV1571IDWG4 (TEXAS INSTRUMENTS INC) 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | TLV1571IDWG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| 封裝: | GREEN, PLASTIC, SOIC-24 |

| 文件頁數(shù): | 23/33頁 |

| 文件大小: | 627K |

| 代理商: | TLV1571IDWG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

TLV1571, TLV1578

2.7 V TO 5.5 V, 1-/8-CHANNEL, 10-BIT,

PARALLEL ANALOG-TO-DIGITAL CONVERTERS

SLAS170D –MARCH 1999 – REVISED JULY 2000

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

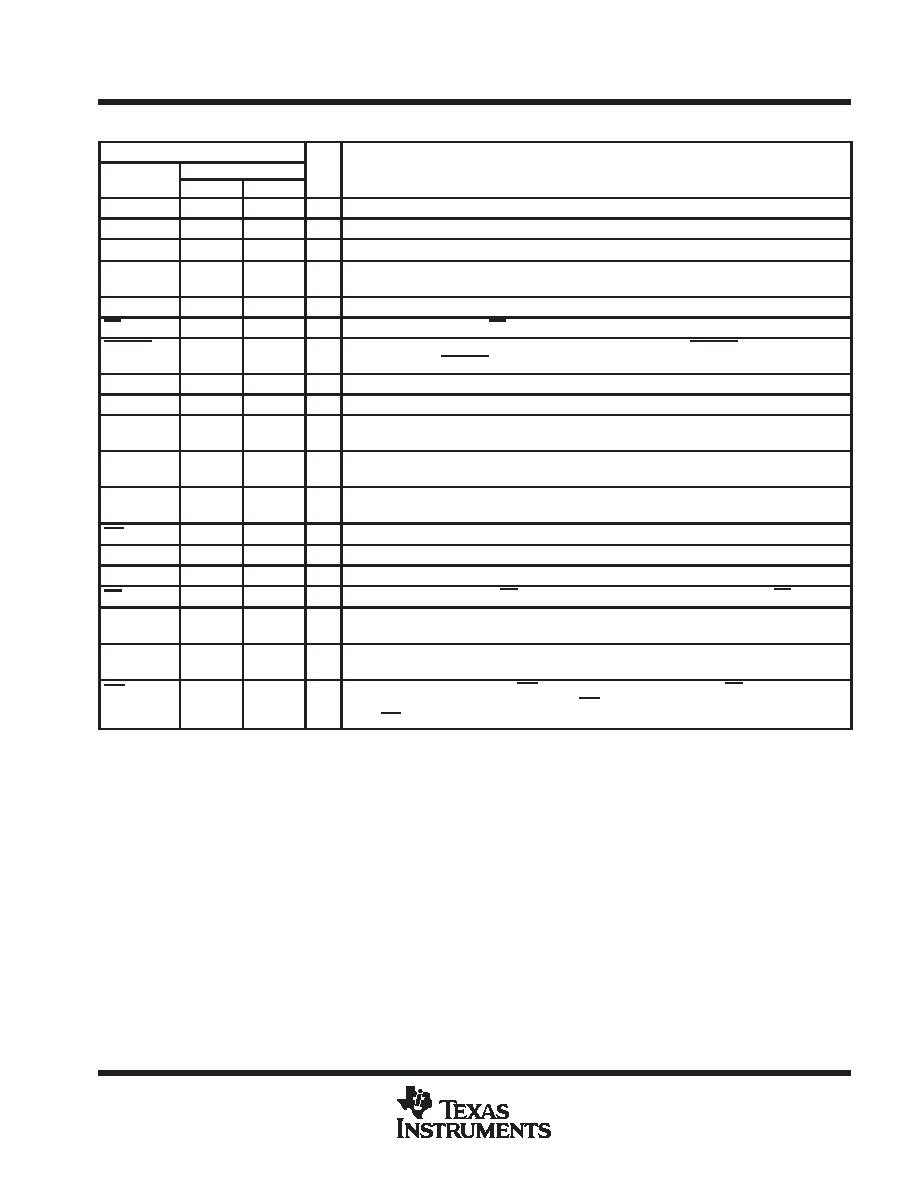

Terminal Functions

TERMINAL

NAME

NO.

I/O

DESCRIPTION

NAME

TLV1571

TLV1578

AGND

21

25

Analog ground

AIN

23

27

I

ADC analog input (used as single analog input channel for TLV1571)

AVDD

22

26

Analog supply voltage, 2.7 V to 5.5 V

CH0 – CH7

–

1– 4,

29–32

I

Analog input channels

CLK

4

8

I

External clock input

CS

1

5

I

Chip select. A logic low on CS enables the TLV1571/ TLV1578.

CSTART

18

22

I

Hardware sample and conversion start input. The falling edge of CSTART starts sampling and

the rising edge of CSTART starts conversion.

DGND

5

9

Digital ground

DVDD

6

10

Digital supply voltage, 2.7 V to 5.5 V

D0 – D7

8 –12,

13 –15

12 –16,

17–19

I/O

Bidirectional 3-state data bus

D8/A0

16

20

I/O

Bidirectional 3-state data bus. D8/A0 along with D9/A1 is used as address lines to access CR0

and CR1 for initialization.

D9/A1

17

21

I/O

Bidirectional 3-state data bus. D9/A1 along with D8/A0 is used as address lines to access CR0

and CR1 for initialization.

INT/EOC

7

11

O

End-of-conversion/interrupt

MO

28

O

On-chip MUX analog output

NC

24

Not connected

RD

3

7

I

Read data. A falling edge on RD enables a read operation on the data bus when CS is low.

REFM

20

24

I

Lower reference voltage (nominally ground). REFM must be supplied or REFM pin must be

grounded.

REFP

19

23

I

Upper reference voltage (nominally AVDD). The maximum input voltage range is determined by

the difference between the voltage applied to REFP and REFM.

WR

2

6

I

Write data. A rising edge on the WR latches in configuration data when CS is low. When using

software conversion start, a rising edge on WR also initiates an internal sampling start pulse.

When WR is tied to ground, the ADC in nonprogrammable (hardware configuration mode).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV1571IPWG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV1571CDWG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV1578CDARG4 | 8-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO32 |

| TLV1571IDW | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV1571CPW | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV1571IPW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit 1.2 MSPS PA RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1571IPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 1-Ch 10-Bit 1.25MSPS 8-Ch DSP/SPI RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1572 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V, 10-BIT, 1.25 MSPS SERIAL ANALOG-TO-DIGITAL CONVERTER WITH AUTO-POWERDOWN |

| TLV1572CD | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit A/D RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1572CDG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 1.25 MSPS 1-Ch DSP RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。