- 您現(xiàn)在的位置:買賣IC網 > PDF目錄383955 > TLE6210 (INFINEON TECHNOLOGIES AG) ABS System IC PDF資料下載

參數資料

| 型號: | TLE6210 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | ABS System IC |

| 中文描述: | ABS系統(tǒng)集成電路 |

| 文件頁數: | 25/35頁 |

| 文件大?。?/td> | 693K |

| 代理商: | TLE6210 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

TLE 6210

TLE 6211

Block Description and Electrical Characteristics

V1.2 Data Sheet

25

2002-08

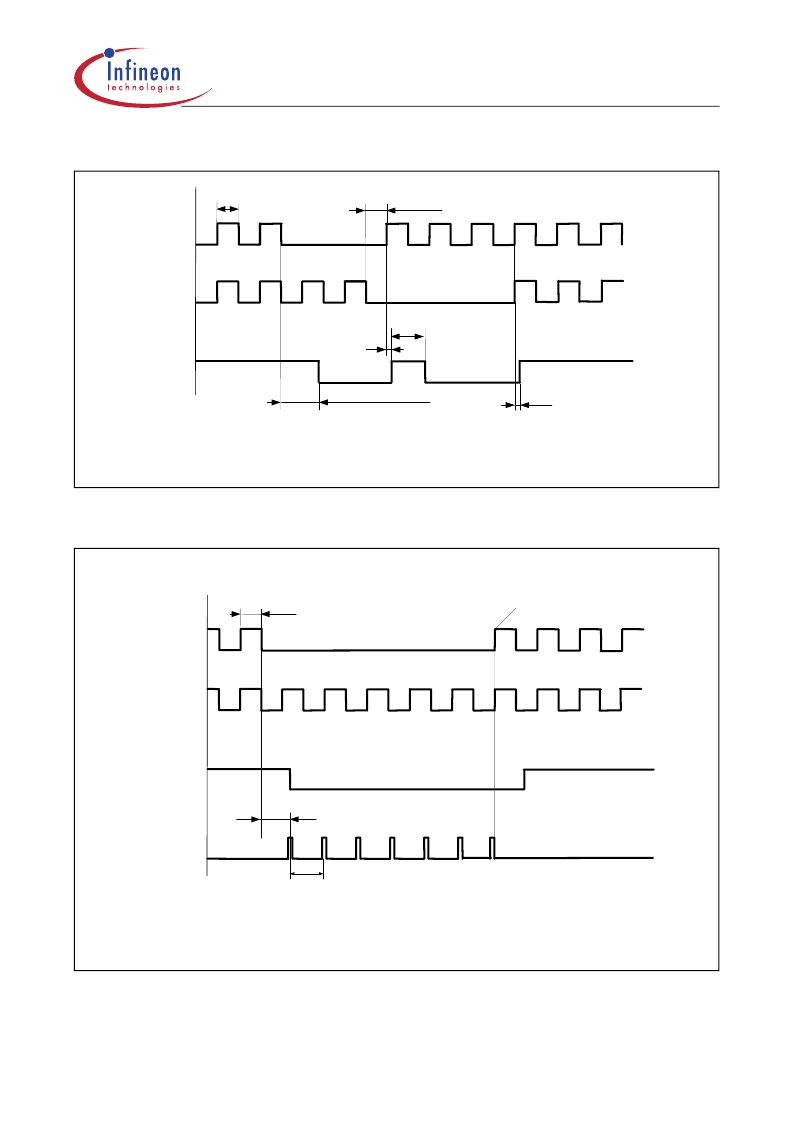

Figure 8

Missing watchdog signals cause EN low

Figure 9

Timing diagram - any watchdog signal missing causes a High signal

at the output "=15" (Counter reset). This signal sets back the logic

1

0

1

0

1

0

15*t

CLK

+ Delay

= 15*t

CLK

+ 3* t

CLK

WD1

WD2

EN

Delay (3* t

CLK

)

t < 15 *t

CLK

Delay (3* t

CLK

)

15*t

CLK

wd-controls-en

AD 03/02

10ms

1

0

1

0

1

0

10ms

WD1

WD2

EN

WD Signal not detected

(15+3) * t

CLK

1

0

Counter Reset

16* t

CLK

wd-missing

AD 03/02

相關PDF資料 |

PDF描述 |

|---|---|

| TLE6210C | ABS System IC |

| TLE6210G | ABS System IC |

| TLE6211 | ABS System IC |

| TLE6211G | ABS System IC |

| TLE6214L | Smart Dual Current Sense Switch |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLE6210C | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ABS System IC |

| TLE6210G | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ABS System IC |

| TLE6211 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ABS System IC |

| TLE6211G | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:ABS System IC |

| TLE6211G-C1 | 制造商:Infineon Technologies AG 功能描述:SP000013647_SYSTEM IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。