- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383954 > TLC34075A-135 (Texas Instruments, Inc.) Color-Palette(135MHz,視頻接口調(diào)色器) PDF資料下載

參數(shù)資料

| 型號: | TLC34075A-135 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Color-Palette(135MHz,視頻接口調(diào)色器) |

| 中文描述: | 顏色調(diào)色板(135MHz,視頻接口調(diào)色器) |

| 文件頁數(shù): | 18/53頁 |

| 文件大?。?/td> | 394K |

| 代理商: | TLC34075A-135 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

2-5

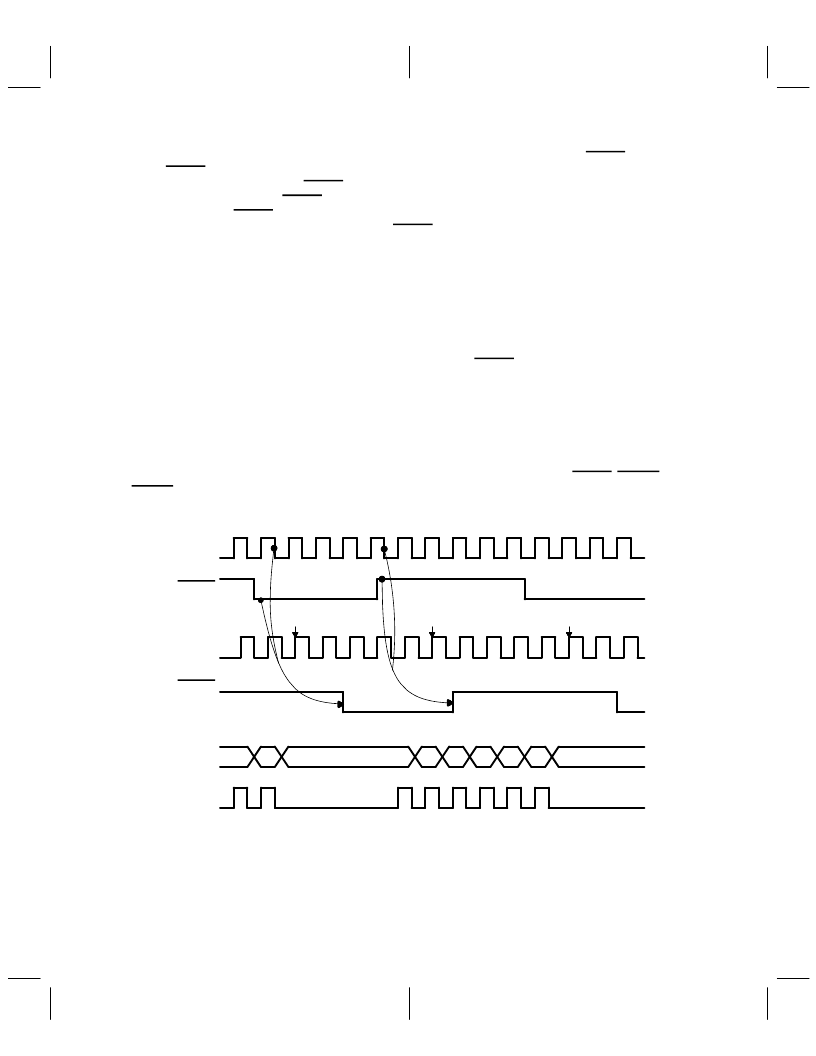

The falling edge of VCLK is used internally by the TLC34075A to sample and latch the BLANK input level.

When BLANK goes low, SCLK is disabled as soon as possible. In other words, if the last SCLK pulse is at

the high level while the sampled BLANK is low, SCLK is allowed to finish its cycle to low level, then SCLK

is held low until the sampled BLANK goes back high to enable it again. The VRAM shift register should be

updated during the BLANK active period, and the first SCLK pulse is used to clock the first valid pixel data

from the VRAM. The internal pipeline delay of the BLANK input is designed to be in phase with data at the

DAC output to the monitors. The logic described above works in situations wherein the SCLK period is

shorter than, equal to, or longer than the VCLK period.

Figure 2–3 shows the case wherein the SSRT (split shift register transfer) function is enabled. One SCLK

pulse with a minimum width of 15 ns is generated from the rising edge at the SFLAG input with specified

delay. This is designed to meet the VRAM timing requirement, and this SCLK pulse replaces the first SCLK

in the regular shift register transfer case as described above. Refer to Section 2.9 for the detailed

explanation of the SSRT function.

The SCLK output waveform may vary at the time that the sampled BLANK input is low. Refer to Appendix C

for details.

2.3.2

VCLK

The VCLK frequency can be selected to be 1/1, 1/2, 1/4, 1/8, 1/16, or 1/32 of that of the dot clock, or it can

be held at a high logic level. The default condition is for VCLK to be held at a high logic level. VCLK is not

used in VGA pass-through mode.

VCLK is used by a GSP or custom-designed control logic to generate control signals (BLANK, HSYNC, and

VSYNC). As can be seen from Figures 2–2, 2–3, 2–4, and 2–5, since the control signals are sampled by

VCLK, it is obvious that VCLK has to be enabled.

2nd

Group

SCLK

at Input Pin

PIXEL DATA

Pipeline Delay)

(Internal Signal

BLANK

for Data Latch)

(Internal LOAD

at Input Pin

BLANK

VCLK

Group

1st

Last Group of Pixel Data

of Pixel Data

Latch Last Group

of Pixel Data

Latch First Group

of Pixel Data

Latch Last Group

3rd

Group

4th

Group

6th

Group

NOTE: Either the SSRT function is disabled (general control register bit 2 = 0), or the SFLAG/NFLAG input is held low

if the SSRT function is enabled (general control register bit 2 = 1).

Figure 2–2. SCLK/VCLK Control Timing (SSRT Disabled,

SCLK Frequency = VCLK Frequency)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC34075A-66 | Color-Palette(66MHz,視頻接口調(diào)色器) |

| TLC34075A-85 | Color-Palette(85MHz,視頻接口調(diào)色器) |

| TLC3544IDWR | 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS |

| TLC3544IPWR | 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS |

| TLC3544IPWRG4 | 5-V ANALOG, 3-/5-V DIGITAL, 14-BIT, 200-KSPS, 4-/8-CHANNELS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH 0-5 V (PSEUDODIFFERENTIAL) INPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC34076 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Video Interface Palette |

| TLC34076-135FN | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC34076-85FN | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC34077 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Video Interface Palette Data Manual |

| TLC34077135FN | 制造商:TI 功能描述:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。