- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98217 > THS10064IDA (TEXAS INSTRUMENTS INC) 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF資料下載

參數(shù)資料

| 型號: | THS10064IDA |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封裝: | GREEN, PLASTIC, TSSOP-32 |

| 文件頁數(shù): | 19/42頁 |

| 文件大小: | 527K |

| 代理商: | THS10064IDA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

THS10064

SLAS255B – DECEMBER 1999 – REVISED DECEMBER 2002

www.ti.com

26

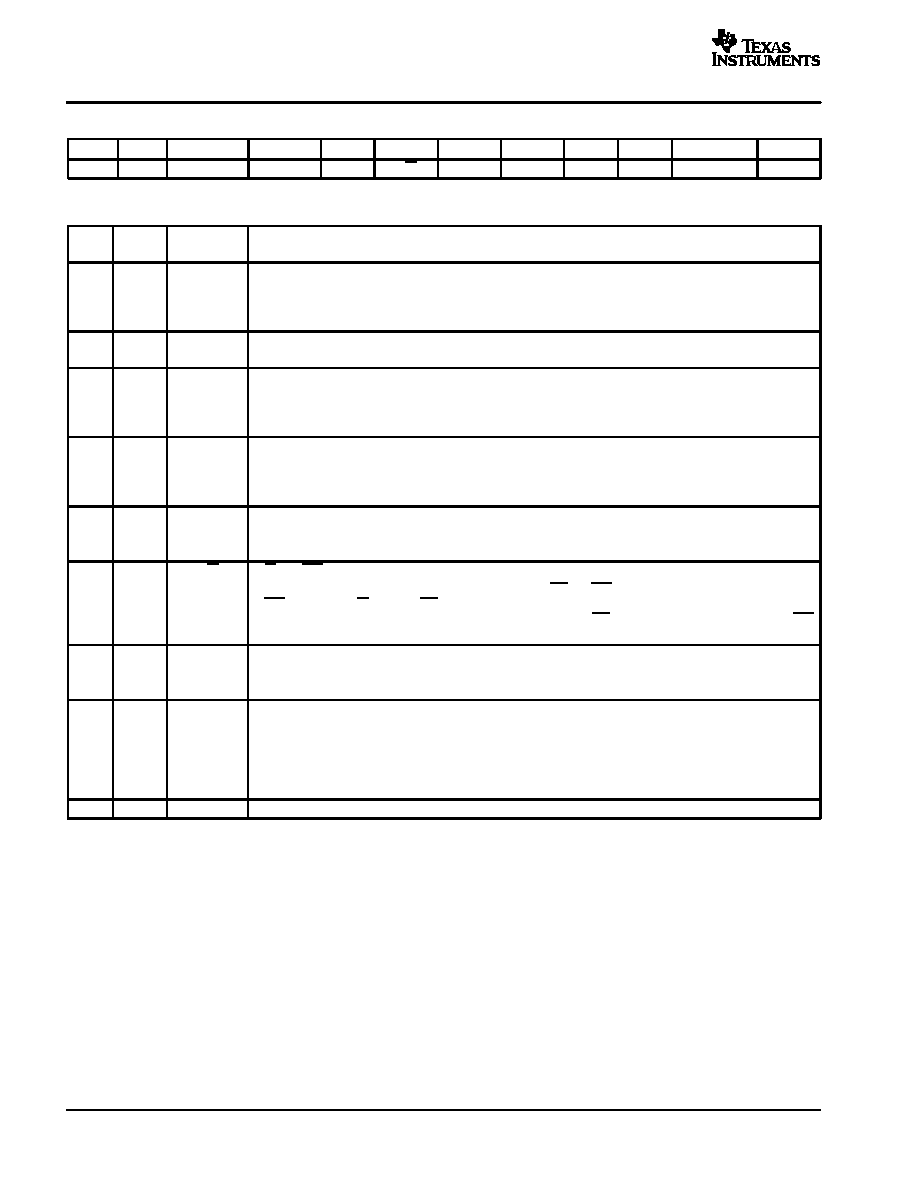

Control Register 1, Write Only (see Table 8)

RA1

RA0

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

1

RESERVED

OFFSET

BIN/2s

R/W

DATA_P

DATA_T

TRIG1

TRIG0

OVFL/FRST

RESET

Table 12. Control Register 1 Bit Functions

BITS

RESET

VALUE

NAME

FUNCTION

0

RESET

Reset

Writing a 1 into this bit resets the device and sets the control register 0 and control register 1 to the reset values.

In addition the FIFO pointer and offset register is reset. After reset, it takes 5 clock cycles until the first value is

converted and written into the FIFO.

1

0

FRST

FRST: FIFO reset

By writing a 1 into this bit, the FIFO is reset.

2, 3

0,0

TRIG0,

TRIG1

FIFO trigger level

Bit 2 and bit 3 of control register 1 are used to set the trigger level for the FIFO. If the trigger level is reached, the

signal DATA_AV (data available) becomes active according to the settings of DATA_T and DATA_P. This

indicates to the processor that the ADC values can be read. Refer to Table 13.

4

1

DATA_T

DATA_AV type

Bit 4 of control register 1 controls whether the DATA_AV signal is a pulse or static (e.g for edge or level sensitive

interrupt inputs). If it is set to 0, the DATA_AV signal is static. If it is set to 1, the DATA_AV signal is a pulse. Refer

to Table 14.

5

1

DATA_P

DATA_AV polarity

Bit 5 of control register 1 controls the polarity of DATA_AV. If it is set to 1, DATA_AV is active high. If it is set to 0,

DATA_AV is active low. Refer to Table 14.

6

0

R/W

R/W, RD/WR selection

Bit 6 of control register 1 controls the function of the inputs RD and WR. When bit 6 in control register 1 is set to

1, WR becomes a R/W input and RD is disabled. From now on a read is signalled with R/W high and a write with

R/W as a low signal. If bit 6 in control register 1 is set to 0, the input RD becomes a read input and the input WR

becomes a write input.

7

0

BIN/2s

Complement select

If bit 7 of control register 1 is set to 0, the output value of the ADC is in twos complement. If bit 7 of

control register 1 is set to 1, the output value of the ADC is in binary format. Refer to Table 3 through Table 6.

8

0

OFFSET

Offset cancellation mode

Bit 8 = 0

→ normal conversion mode

Bit 8 = 1

→ offset calibration mode

If a 1 is written into bit 8 of control register 1, the device internally sets the inputs to zero and does a conver-

sion. The conversion result is stored in an offset register and subtracted from all conversions in order to

reduce the offset error.

9

0

RESERVED

Always write 0.

FIFO TRIGGER LEVEL

Bit 2 and bit 3 (TRIG1, TRIG0) of control register 1 are used to set the trigger level of the FIFO (see Table 13). If the

trigger level is reached, the DATA_AV (data available) signal becomes active according to the setting of the signal

DATA_AV to indicate to the processor that the ADC values can be read.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS10064CDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064IDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS10064IDAG4 | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDA | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1007CDAR | 4-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS10064IDAG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10B 6 MSPS ADC Quad Ch. DSP/uP Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1007 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 4 ANALOG INPUT, 6-MSPS, SIMULATANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1007CDA | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 6MSPS Simult Sampling Quad Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1007CDAG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 6MSPS Simult Sampling Quad Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1007CDAR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 4 ANALOG INPUT, 6-MSPS, SIMULATANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。