- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383878 > TAS5036BPFCRG4 (Texas Instruments, Inc.) Six Channel Digital Audio PWM Processor PDF資料下載

參數(shù)資料

| 型號: | TAS5036BPFCRG4 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Six Channel Digital Audio PWM Processor |

| 中文描述: | 六通道數(shù)字音頻PWM處理器 |

| 文件頁數(shù): | 34/58頁 |

| 文件大?。?/td> | 745K |

| 代理商: | TAS5036BPFCRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

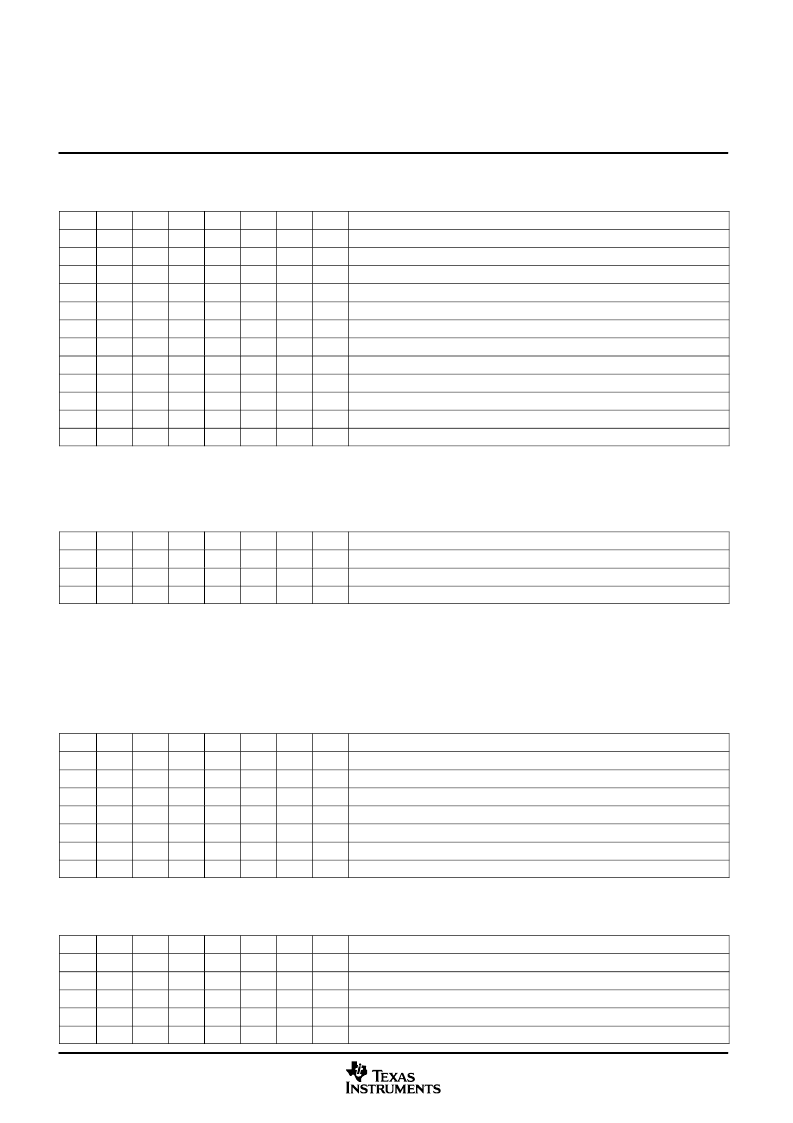

Serial Control Interface Register Definitions

28

SLES073

—

February 2003

TAS5036B

3.6

Automute Delay Register (x05)

Table 3

–

7. Automute Delay Register

D7

D6

D5

D4

D3

D2

D1

D0

FUNCTION

0

0

0

0

-

-

-

-

Unused

-

-

-

-

-

-

-

-

-

-

-

-

0

0

0

0

Set automute delay at 5 ms

-

-

-

-

0

0

0

1

Set automute delay at 10 ms

-

-

-

-

0

0

1

0

Set automute delay at 15 ms

-

-

-

-

0

0

1

1

Set automute delay at 20 ms

-

-

-

-

0

1

0

0

Set automute delay at 25 ms

-

-

-

-

0

1

0

1

Set automute delay at 30 ms

-

-

-

-

0

1

1

0

Set automute delay at 35 ms

-

-

-

-

0

1

1

1

Set automute delay at 40 ms

-

-

-

-

1

-

-

0

Set automute delay at 45 ms

-

-

-

-

1

-

-

1

Set automute delay at 50 ms

3.7

DC-Offset Control Registers (x06

–

x0B)

Channels 1, 2, 3, 4, 5, and 6 are mapped into (x06, x07, x08, x09, x0A, and x0B).

Table 3

–

8. DC-Offset Control Registers

D7

D6

D5

D4

D3

D2

D1

D0

FUNCTION

1

0

0

0

0

0

0

0

Maximum correction for positive dc offset (

–

1.56% FS)

0

0

0

0

0

0

0

0

No dc-offset correction

0

1

1

1

1

1

1

1

Maximum correction for negative dc offset (1.56% FS)

3.8

Interchannel Delay Registers (x0C

–

x11)

Channels 1, 2, 3, 4, 5, and 6 are mapped into (x0C, x0D, x0E, x0F, x10, and x11).

The first channel delay is set at 0. Each subsequent channel has a default value that is 76 DCLKs larger than

the preceding channel.

Table 3

–

9. Six Interchannel Delay Registers

D7

D6

D5

D4

D3

D2

D1

D0

FUNCTION

0

0

0

0

0

0

0

0

Minimum absolute delay, 0 DCLK cycles, default for channel 1

0

1

0

0

1

1

0

0

Default for channel 2

1

0

0

1

1

0

0

0

Default for channel 3

1

1

1

0

0

1

0

0

Default for channel 4

0

0

1

1

0

0

0

0

Default for channel 5

0

1

1

1

1

1

0

0

Default for channel 6

1

1

1

1

1

1

1

1

Maximum absolute delay, 255 DCLK cycles

3.9

ABD Delay Register (x12)

Table 3

–

10. ABD Delay Register

D7

D6

D5

D4

D3

D2

D1

D0

FUNCTION

0

0

0

-

-

-

-

-

Unused

-

-

-

-

-

-

-

-

-

-

-

0

0

0

0

0

Minimum ABD delay, 0 DLCK cycles

-

-

-

1

0

0

0

1

Default ABD delay, 17 DLCK cycles

-

-

-

1

1

1

1

1

Maximum ABD delay, 31 DLCK cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TAS5100ADAP | Single Audio Amplifier |

| TAS5100AIDAPR | Single Audio Amplifier |

| TAS5100ADAPR | Single Audio Amplifier |

| TAS5100AIDAP | Single Audio Amplifier |

| TAS5110ADADR | PurePath Digital AMPLIFIER TAS5110A 50-W DIGITAL AMPLIFIER POWER STAGE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS5036CPAG | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SIX CHANNEL DIGITAL AUDIO PWM PROCESSOR |

| TAS5036IPFC | 功能描述:音頻 DSP Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| TAS5036IPFCG4 | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| TAS5036IPFCR | 功能描述:音頻 DSP Dig Aud PWM Proc RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| TAS5036IPFCRG4 | 功能描述:音頻 DSP Digital Audio PWM Processor RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。