- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383878 > TAS5036AIPFC (Texas Instruments, Inc.) Six Channel Digital Audio PWM Processor PDF資料下載

參數(shù)資料

| 型號: | TAS5036AIPFC |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Six Channel Digital Audio PWM Processor |

| 中文描述: | 六通道數(shù)字音頻PWM處理器 |

| 文件頁數(shù): | 14/62頁 |

| 文件大小: | 790K |

| 代理商: | TAS5036AIPFC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

Architecture Overview

8

SLES061B—November 2002—Revised January 2004

TAS5036A

If the master clock input can encounter high clock or low clock period of less than 20 ns while the data rates

are changing, then RESET should be applied during this time. There are two recommended control

procedures for this case, depending upon whether the DBSPD terminal or the serial control interface is used.

These control sequences are shown in Section 4.

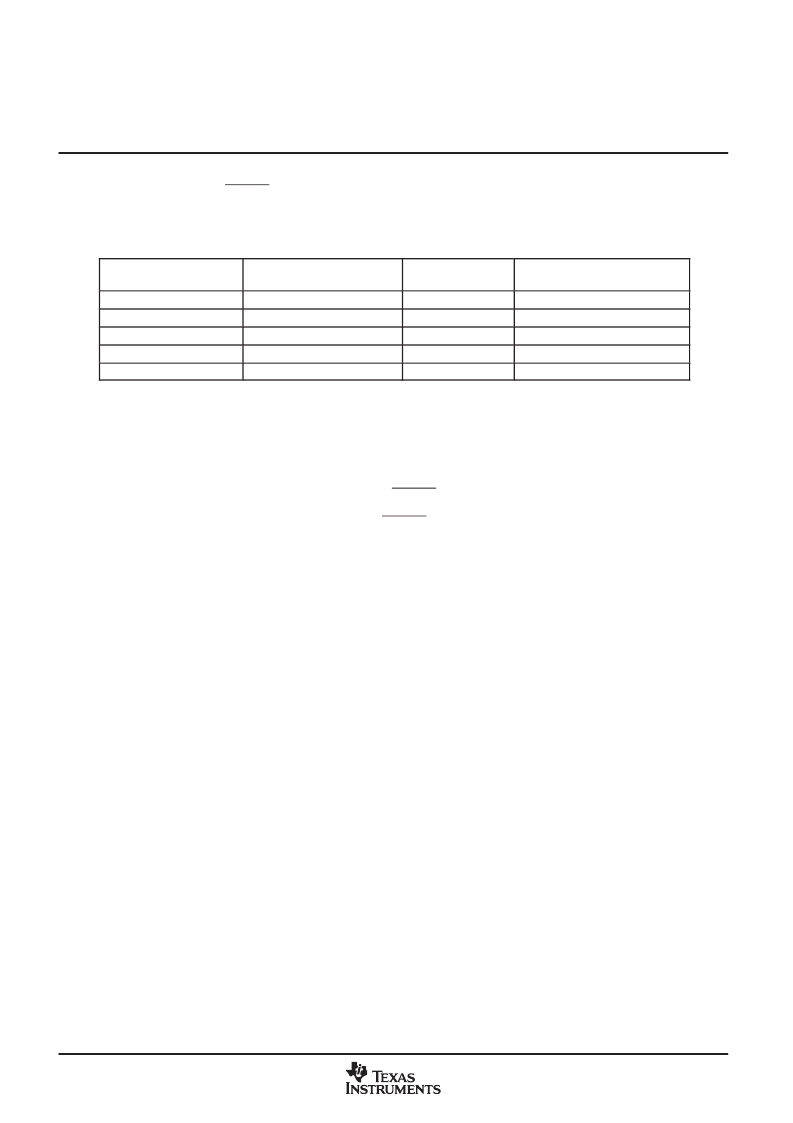

Table 21. Normal-Speed, Double-Speed, and Quad-Speed Operation

QUAD-SPEED CONTROL

REGISTER BIT

DBSPD TERMINAL OR

CONTROL REGISTER BIT

MODE

SPEED SELECTION

0

0

Master or slave

Normal speed

0

1

Master or slave

Double speed

1

0

Master or slave

Quad speed

0

0

Slave

Quad speed if MCLK_IN = 128Fs

1

1

Master or slave

Error

2.1.2 Clock Master/Slave Mode (M_S)

Clock master and slave mode can be invoked using the M_S (master slave) terminal.

This terminal specifies the default mode that is set immediately following a device RESET. The serial data

interface setting permits the clock generation mode to be changed during normal operation.

The transition to master mode occurs following a RESET when M_S terminal has a logic high applied.

The transition to slave mode occurs following a RESET when M_S terminal has a logic low applied.

2.1.3 Clock Master Mode

When M_S = 1 following a RESET, the TAS5036A provides the master clock, SCLK, and LRCLK to the rest

of the system. In the master mode, the TAS5036A outputs the audio system clocks MCLK_OUT, SCLK, and

LRCLK.

The TAS5036A device generates these clocks plus its internal clocks from the internal phase-locked loop

(PLL). The reference clock for the PLL can be provided by either an external clock source (attached to

XTAL_IN) or a crystal (connected across terminals XTAL_IN and XTAL_OUT). The external source attached

to MCLK_IN is 256 times (128 in quad mode) the data sample rate (Fs). The SCLK frequency is 64 times the

data sample rate and the SCLK frequency of 48 times the data sample rate is not supported in the master

mode. The LRCLK frequency is the data sample rate.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TAS5036AIPFCG4 | Six Channel Digital Audio PWM Processor |

| TAS5036AIPFCR | Six Channel Digital Audio PWM Processor |

| TAS5036AIPFCRG4 | Six Channel Digital Audio PWM Processor |

| TAS5036APFC | Six Channel Digital Audio PWM Processor |

| TAS5036APFCG4 | Six Channel Digital Audio PWM Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS5036AIPFCG4 | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| TAS5036AIPFCR | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| TAS5036AIPFCRG4 | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| TAS5036APFC | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

| TAS5036APFCG4 | 功能描述:音頻放大器 Digital Audio PWM Processor RoHS:否 制造商:STMicroelectronics 產(chǎn)品:General Purpose Audio Amplifiers 輸出類型:Digital 輸出功率: THD + 噪聲: 工作電源電壓:3.3 V 電源電流: 最大功率耗散: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TQFP-64 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。