- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385873 > STA120D (意法半導體) DIGITAL AUDIO INTERFACE RECEIVER PDF資料下載

參數(shù)資料

| 型號: | STA120D |

| 廠商: | 意法半導體 |

| 英文描述: | DIGITAL AUDIO INTERFACE RECEIVER |

| 中文描述: | 數(shù)字音頻接口接收機 |

| 文件頁數(shù): | 7/15頁 |

| 文件大小: | 183K |

| 代理商: | STA120D |

7/15

STA120

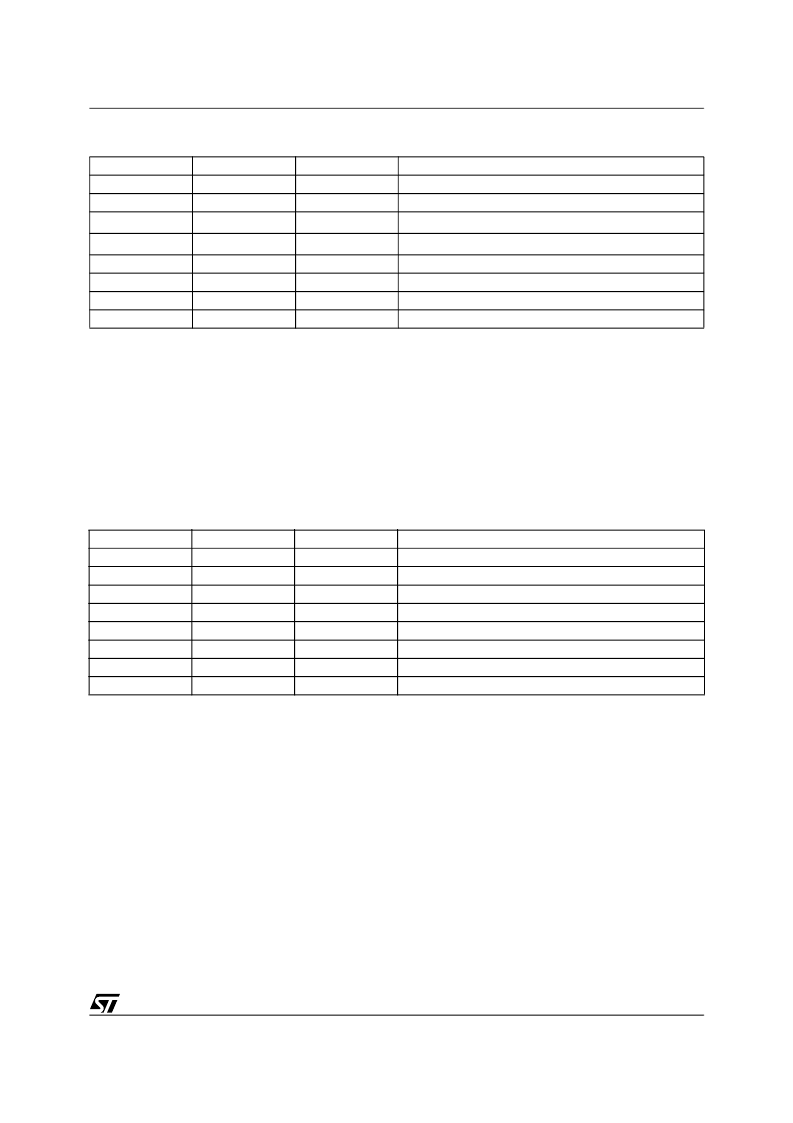

Table 1. Normal Audio Port Modes (M3 = 0)

Special Modes (M3 = 1)

When M3 is high, the special audio modes described in Table 2 are selected via M2, M1, and M0. In for-

mats 8, 9, and 10, SCK, FSYNC, and SDATA are the same as in formats 0, 1, and 2 respectively; however,

the recovered data is output as is even if ERF is high, indicating an error. (In modes 0-2 the previous valid

sample is output).

When out of lock invalid data are sent to the output and the ERF pin goes high.

Format 11 is similar to format 0 except that SCK is an input and FSYNC is an output.

In this mode FSYNC and SDATA are synchronized to the incoming SCK, This mode may be useful when

writing data to storage.

Table 2. Special Audio Port Modes (M3 = 1)

Format 12 is similar to format 7 except that SDATA is the entire data word received from the transmission

line including the C, U, V, and P bits, with zeros in place of the preamble. In format 13 SDATA contains

the entire biphase encoded data from the transmission line including the preamble, and SCK is twice the

normal frequency.

The normal two frame delay of data from input to output is reduced to only a few bit periods in formats 12

and 13. However, the C, U, V bits and error codes follow their normal pathways and therefore follow the

output data by nearly two frames. Figure 4.... illustrates formats 12 and 13. Format 14 is reserved and not

presently used, and format 15 causes the STA120 to go into a reset state. While in reset all outputs will

be inactive except MCK. The STA120 incorporates a Power-on Reset to avoid a Reset at power-up.

C, U, VERF, ERF, and CBL Serial Outputs

The C and U bits and CBL are output one SCK period prior to the active edge of FSYNC in all serial port

formats except 2, 3 and 10 (I

2

S modes). The active edge of FSYNC may be used to latch C, U, and CBL

externally. In formats 2, 3 and 10, the C and U bits and CBL are updated with the active edge of FSYNC.

The validity + error flag (VERF) and the error flag (ERF) are always updated at the active edge of FSYNC.

M2

0

0

0

M1

0

0

1

M0

0

1

0

Format

0 - Out, L/R, 16-24 Bits

1 - In, L/R, 16-24 Bits

2 - Out, L/R, I

2

S Compatible

3 - In, L/R, I

2

S Compatible

4 - Out, WSYNC, 16-24 Bits

5 - Out, L/R, 16 Bits LSBJ

6 - Out, L/R, 18 Bits LSBJ

7 - Out, L/R, MSB Last

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

M2

0

0

0

0

1

1

1

1

M1

0

0

1

1

0

0

1

1

M0

0

1

0

1

0

1

0

1

Format

8 - Format 0 - No repeat on error

9 - Format 1 - No repeat on error

10 - Format 2 - No repeat on error

11 - Format 0 - Async. SCK input

12 - Received NRZ Data

13 - Received Bi-phase Data

14 - Reserved

15 - STA120 Reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STA2051 | 32-BIT SINGLE CHIP BASEBAND CONTROLLER FOR GPS AND TELEMATIC APPLICATIONS |

| STAC9204X5NBEYYX | 4-CHANNEL HD AUDIO CODEC WITH QUAD DIGITAL MICROPHONE INTERFACE |

| STAC9205D3TAEYYXR | 4-CHANNEL HD AUDIO CODEC WITH QUAD DIGITAL MICROPHONE INTERFACE |

| STAC9205D5NBEYYX | 4-CHANNEL HD AUDIO CODEC WITH QUAD DIGITAL MICROPHONE INTERFACE |

| STAC9205D5NBEYYXR | 4-CHANNEL HD AUDIO CODEC WITH QUAD DIGITAL MICROPHONE INTERFACE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| STA120D13TR | 功能描述:音頻 DSP Digital Audio Intrfc RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| STA120DJ | 制造商:STMicroelectronics 功能描述:DGTL AUD INTRFC RCVR 28SOIC - Rail/Tube |

| STA120DJ13TR | 功能描述:音頻 DSP Digital audio interface receiver RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風格: 封裝 / 箱體: 封裝:Tube |

| STA1210 | 制造商:M.E.C. Relays 功能描述: |

| STA1225 | 制造商:M.E.C. Relays 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。