- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383837 > ST16C580CJ44 (EXAR CORP) UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER PDF資料下載

參數(shù)資料

| 型號(hào): | ST16C580CJ44 |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| 中文描述: | 1 CHANNEL(S), 1.5M bps, SERIAL COMM CONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁(yè)數(shù): | 10/41頁(yè) |

| 文件大小: | 244K |

| 代理商: | ST16C580CJ44 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

ST16C580

10

Rev. 1.20

FIFO Operation

The 16 byte transmit and receive data FIFO’s are

enabled by the FIFO Control Register (FCR) bit-0.

With 16C550 devices, the user can set the receive

trigger level but not the transmit trigger level. The 580

provides independent trigger levels for both receiver

and transmitter. To remain compatible with

ST16C550, the transmit interrupt trigger level is set to

1 following a reset. It should be noted that the user can

set the transmit trigger levels by writing to the FCR

register, but activation will not take place until EFR bit-

4 is set to a logic 1. The receiver FIFO section includes

a time-out function to ensure data is delivered to the

external CPU. An interrupt is generated whenever the

Receive Holding Register (RHR) has not been read

following the loading of a character or the receive

trigger level has not been reached. (see hardware flow

control for a description of this timing).

Hardware Flow Control

When automatic hardware flow control is enabled, the

580 monitors the -CTS pin for a remote buffer overflow

indication and controls the -RTS pin for local buffer

overflows. Automatic hardware flow control is se-

lected by setting bits 6 (RTS) and 7 (CTS) of the EFR

register to a logic 1. If -CTS transitions from a logic 0

to a logic 1 indicating a flow control request, ISR bit-

5 will be set to a logic 1 (if enabled via IER bit 6-7), and

the 580 will suspend TX transmissions as soon as the

stop bit of the character in process is shifted out.

Transmission is resumed after the -CTS input returns

to a logic 0, indicating more data may be sent.

With the Auto RTS function enabled, an interrupt is

generated when the receive FIFO reaches the pro-

grammed trigger level. The -RTS pin will not be forced

to a logic 1 (RTS Off), until the receive FIFO reaches

the next trigger level

.

However, the -RTS pin will

return to a logic 0 after the data buffer (FIFO) is

unloaded to the next trigger level below the pro-

grammed trigger level. However, under the above

described conditions the 580 will continue to accept

data until the receive FIFO is full.

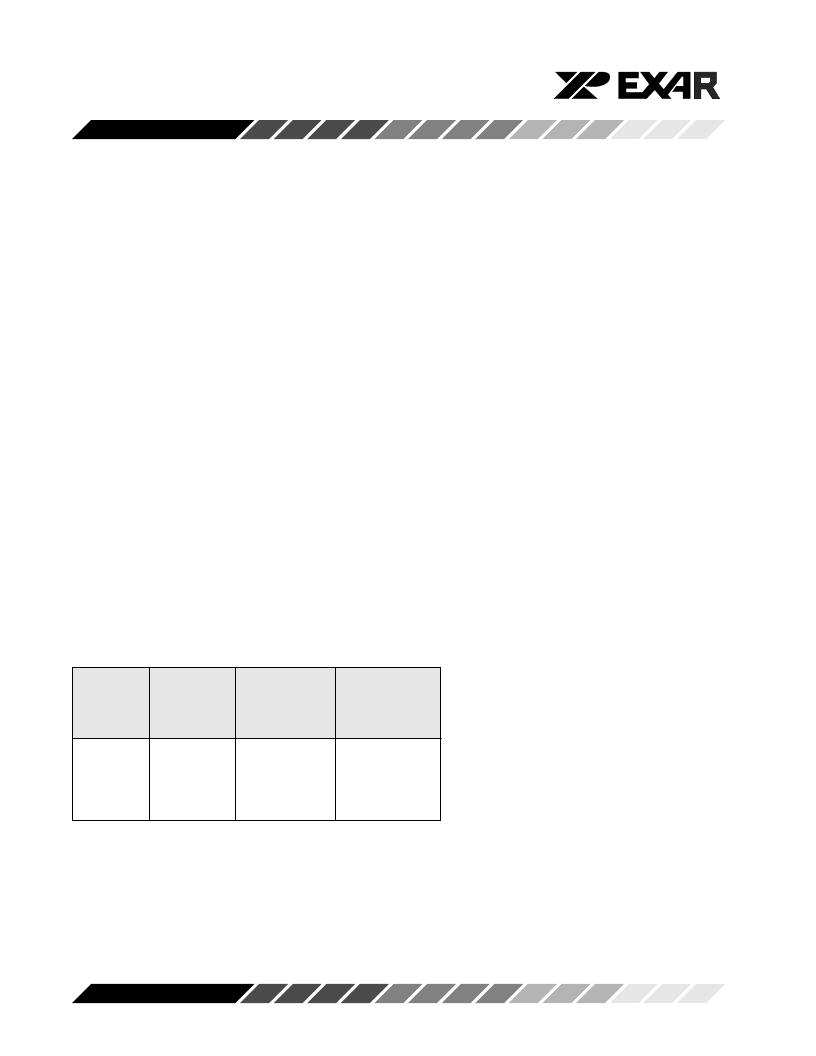

Selected

Trigger

Level

(characters)

INT

Pin

-RTS

Logic “1”

(characters)

-RTS

Logic “0”

(characters)

Activation

1

4

8

14

1

4

8

14

4

8

14

14

0

1

4

8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST16C654CJ68 | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| ST16C654CQ100 | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| ST16C654 | Linear Voltage Regulator IC; Output Current Max:350mA; Supply Voltage Max:6V; Package/Case:8-TSSOP; Output Current:600mA; Output Voltage:5V; Current Rating:30.05A; Leaded Process Compatible:No; Output Voltage Max:5V |

| ST16C654CQ64 | 2.97V TO 5.5V QUAD UART WITH 64-BYTE FIFO |

| ST16C654D | Voltage Regulator IC; Package/Case:8-MSOP; Output Current:300mA; Output Voltage:3.3V; Supply Voltage Max:6V; Current Rating:300mA; Leaded Process Compatible:No; Output Current Max:300mA; Output Voltage Max:3.3V RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST16C580CP40 | 制造商:EXAR 制造商全稱:EXAR 功能描述:UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

| ST16C580CQ-0A-EVB | 功能描述:界面開發(fā)工具 Supports C580 48 ld TQFP, ISA Interface RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| ST16C580CQ48 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Exar Corporation 功能描述: |

| ST16C580CQ48-F | 功能描述:UART 接口集成電路 UART W/16BYTE FIFO RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| ST16C580IJ44 | 制造商:EXAR 制造商全稱:EXAR 功能描述:UART WITH 16-BYTE FIFO’s AND INFRARED (IrDA) ENCODER/DECODER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。