- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄10784 > SP510EM-L (Exar Corporation)IC TXRX MULTIPROTOCOL HS 100LQFP PDF資料下載

參數(shù)資料

| 型號: | SP510EM-L |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 26/37頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX MULTIPROTOCOL HS 100LQFP |

| 特色產(chǎn)品: | SP510 Ultra High Speed 52Mbps 8-Channel Multi-Protocol Transceiver |

| 標(biāo)準包裝: | 90 |

| 類型: | 收發(fā)器 |

| 驅(qū)動器/接收器數(shù): | 8/8 |

| 規(guī)程: | 多協(xié)議 |

| 電源電壓: | 5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-LQFP |

| 供應(yīng)商設(shè)備封裝: | 100-LQFP(14x14) |

| 包裝: | 托盤 |

| 配用: | 1016-1195-ND - EVAL BOARD FOR SP510 |

| 其它名稱: | 1016-1196 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

SP510

32

ULTRA HIGH SPEED MULTIPROTOCOL TRANSCEIVER

REV. 1.0.1

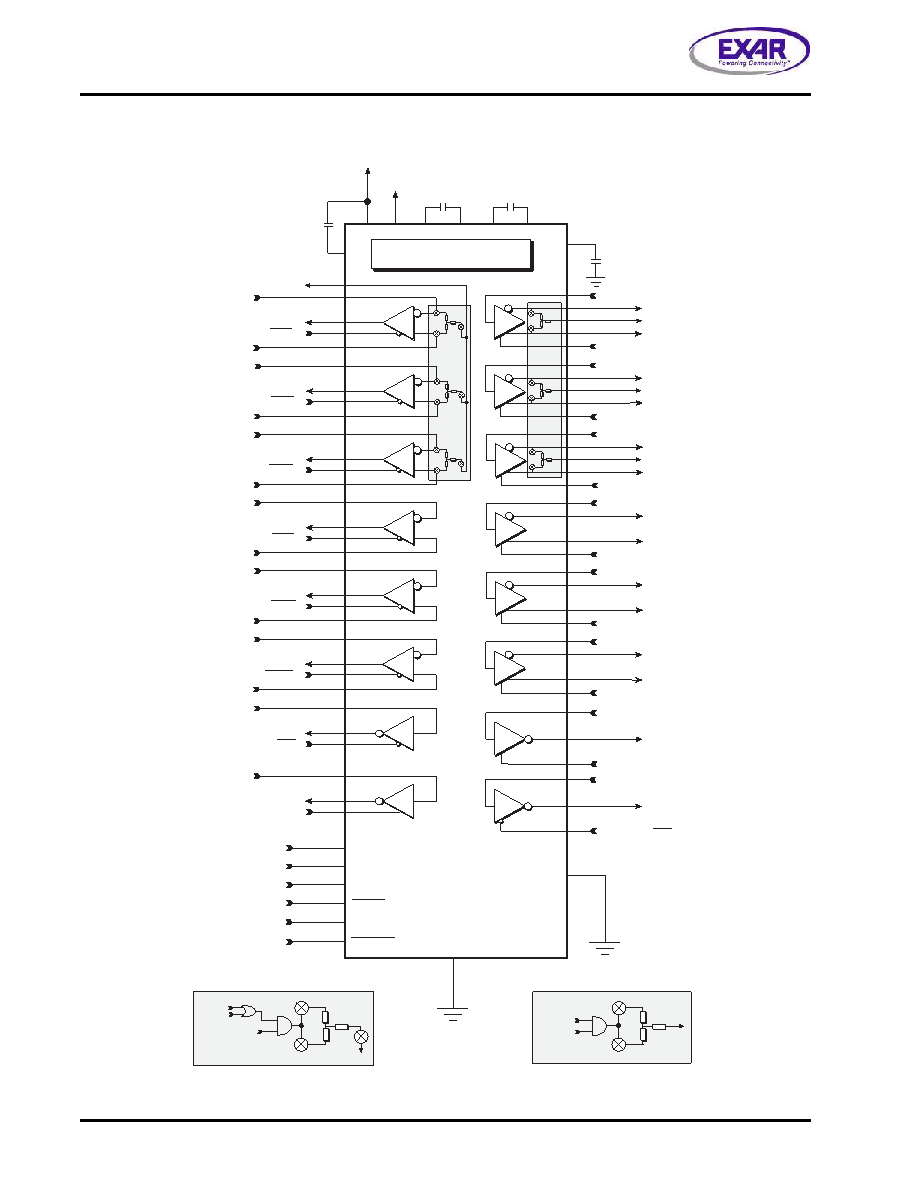

FIGURE 45. FUNCTIONAL DIAGRAM

TxD

SD(a)

V35TGND1

SD(b)

SDEN

VCC

VDD

C1-

VSS

C1+

+5V (decoupling capacitor not shown)

1μF

Regulated Charge Pump

SP510

TxCE

TT(a)

V35TGND2

TT(b)

TTEN

ST

ST(a)

V35TGND3

ST(b)

STEN

RD(a)

RxD

RDEN

RD(b)

RT(a)

RxC

RTEN

RT(b)

TxC(a)

TxC

TxCEN

TxC(b)

CS(a)

CTS

CSEN

CS(b)

DM(a)

DSR

DMEN

DM(b)

RRT(a)

DCD_DTE

RRTEN

RRT(b)

TM(a)

TM

TMEN

RTS

RS(a)

RS(b)

RSEN

DTR

TR(a)

TR(b)

TREN

DCD_DCE

RRC(a)

RRC(b)

RRCEN

LL

LL(a)

LLEN

C2-

C2+

GND

D0

D1

D2

TERM-OFF

D-LATCH

V.10-GND

V.35 MODE

TX ENABLE

51ohms

124ohms

V.35 DRIVER TERMINATION NETWORK

V.35 MODE

RX ENABLE

51ohms

124ohms

RECEIVER TERMINATION NETWORK

V.11 MODE

RL

RL(a)

RLEN

IC

RI

ICEN

V35RGND

LOOPBACK

72

69

70

67

66

73

46

48

36

11

47

50

37

12

49

53

38

13

51

55

39

14

54

57

40

15

56

60

41

16

59

61

42

17

62

43

18

19

20

21

23

22

27

28

97

99

100

3

29

92

94

95

4

30

87

89

90

5

31

83

85

6

32

75

78

7

33

81

79

8

34

65

9

35

63

10

58

VCC pins (26, 64, 71, 77, 80, 84, 88, 93, 98)

GND pins (2, 25, 44, 52, 68, 74, 82, 86, 91, 96)

N.C. pins (24 and 76)

1μF

Logic Voltage

VL

VL pins (1 and 46)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD5334BRUZ-REEL | IC DAC 8BIT QUAD VOUT 24TSSOP |

| XRT7295ATIW-F | IC LINE RCVR 20SOJ |

| VI-BNW-MX-F1 | CONVERTER MOD DC/DC 5.5V 75W |

| LTC2846IG#PBF | IC TXRX 3.3V MULTIPROTCOL 36SSOP |

| VI-JTY-MW-S | CONVERTER MOD DC/DC 3.3V 66W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SP-511076-DSGO | 制造商:Chenbro Micom Usa, Inc. 功能描述:PANEL PC - Bulk |

| SP-511091-SUT | 制造商:Chenbro Micom Usa, Inc. 功能描述:SAMPLE AVNET / SUTUS GW310 - Bulk |

| SP-511094-GB BZL | 制造商:Chenbro Micom Usa, Inc. 功能描述:BEZEL GREENBYTE 3U ALUM COLOR - Bulk |

| SP511P | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:LIQUID CRYSTAL DISPLAYS(STANDARD PRODUCTS) |

| SP-512001-BZL | 制造商:Chenbro Micom Usa, Inc. 功能描述:BEZEL 2U CARBONITE W/ BACK LIGHT, BLK, SR2600- - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。