- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98120 > SN74LV166APWT (TEXAS INSTRUMENTS INC) LV/LV-A/LVX/H SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LV166APWT |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 計(jì)數(shù)移位寄存器 |

| 英文描述: | LV/LV-A/LVX/H SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| 封裝: | GREEN, PLASTIC, TSSOP-16 |

| 文件頁(yè)數(shù): | 12/19頁(yè) |

| 文件大小: | 588K |

| 代理商: | SN74LV166APWT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

SN54LV166A, SN74LV166A

8BIT PARALLELLOAD SHIFT REGISTERS

SCLS456C FEBRUARY 2001 REVISED APRIL 2005

2

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

description/ordering information (continued)

The ’LV166A parallel-in or serial-in, serial-out registers feature gated clock (CLK, CLK INH) inputs and an

overriding clear (CLR) input. The parallel-in or serial-in modes are established by the shift / load (SH/LD) input.

When high, SH/LD enables the serial (SER) data input and couples the eight flip-flops for serial shifting with each

clock (CLK) pulse. When low, the parallel (broadside) data inputs are enabled, and synchronous loading occurs

on the next clock pulse. During parallel loading, serial data flow is inhibited. Clocking is accomplished on the

low-to-high-level edge of CLK through a 2-input positive-NOR gate, permitting one input to be used as a

clock-enable or clock-inhibit function. Holding either CLK or CLK INH high inhibits clocking; holding either low

enables the other clock input. This allows the system clock to be free running, and the register can be stopped

on command with the other clock input. CLK INH should be changed to the high level only when CLK is high.

CLR overrides all other inputs, including CLK, and resets all flip-flops to zero.

These devices are fully specified for partial-power-down applications using Ioff. The Ioff circuitry disables the

outputs, preventing damaging current backflow through the devices when they are powered down.

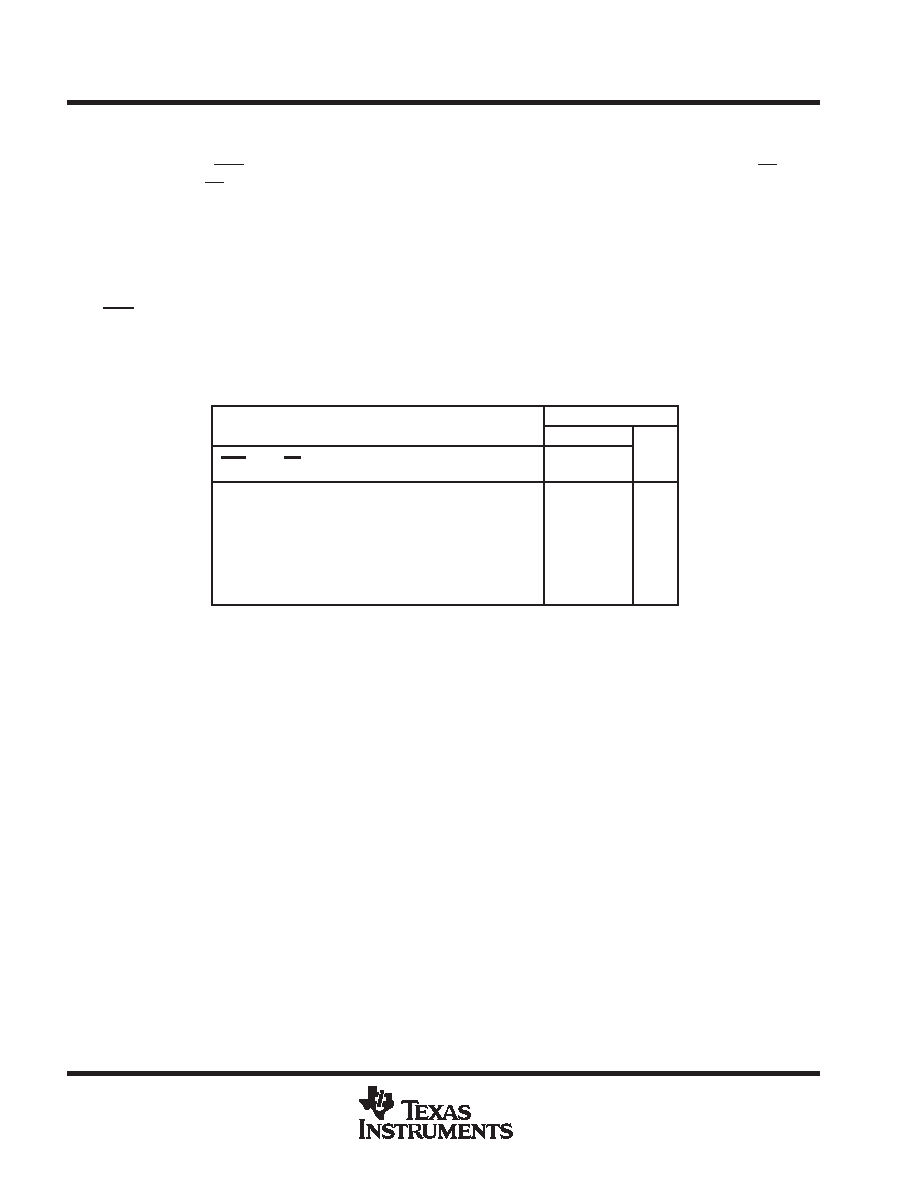

FUNCTION TABLE

INPUTS

OUTPUTS

INPUTS

INTERNAL

CLR

SH/LD

CLK INH

CLK

SER

PARALLEL

A...H

QA

QB

QH

L

X

L

H

XL

L

X

QA0

QB0

QH0

H

LL

↑

X

a ...h

a

bh

H

HL

↑

HX

H

QAn

QGn

H

HL

↑

LX

L

QAn

QGn

H

X

H

↑

X

QA0

QB0

QH0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74LV166APWTE4 | LV/LV-A/LVX/H SERIES, 8-BIT RIGHT PARALLEL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| SN74LV174ADBR | LV/LV-A/LVX/H SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO16 |

| SN74LV174ADE4 | LV/LV-A/LVX/H SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO16 |

| SN74LV174AD | LV/LV-A/LVX/H SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO16 |

| SN74LV174APWE4 | LV/LV-A/LVX/H SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LV166APWTE4 | 功能描述:計(jì)數(shù)器移位寄存器 8-Bit Parallel-Load Shift Register RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LV166APWTG4 | 功能描述:計(jì)數(shù)器移位寄存器 Parallel Load 8B Shift Registers RoHS:否 制造商:Texas Instruments 計(jì)數(shù)器類型: 計(jì)數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時(shí)間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| SN74LV174AD | 功能描述:觸發(fā)器 Hex w/ Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| SN74LV174ADBR | 功能描述:觸發(fā)器 Hex D-Type Flip-Flop With Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| SN74LV174ADBRE4 | 功能描述:觸發(fā)器 Hex D-Type Flip-Flop With Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。