- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373410 > SMAJ50A (意法半導(dǎo)體) 9-Bit Odd/Even Parity Generator/Checker 14-SOIC -55 to 125 PDF資料下載

參數(shù)資料

| 型號: | SMAJ50A |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 9-Bit Odd/Even Parity Generator/Checker 14-SOIC -55 to 125 |

| 中文描述: | TRANSILTM |

| 文件頁數(shù): | 2/4頁 |

| 文件大?。?/td> | 336K |

| 代理商: | SMAJ50A |

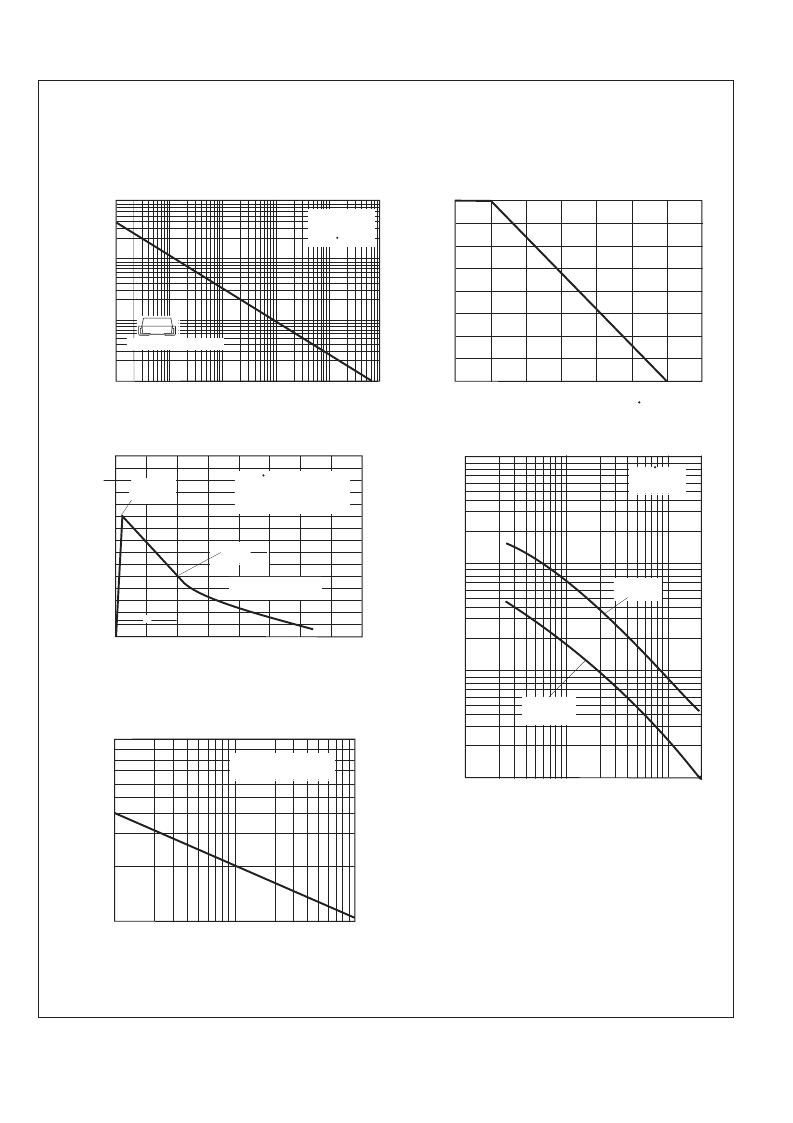

RATING AND CHARACTERISTIC CURVES (SMAJ SERIES)

P

,

P

I

,

P

C

J

FIG.1-PEAK PULSE POWER DERATING CURVE

0.1 s 1.0 s 10 s 100 s 1.0ms 10ms

0.1

1.0

10

100

td, PULSE WIDTH, sec.

Non-Repetitive

Pulse Waveform

Shown in Fig. 3

T =25 C

A

FIG.2-PULSE DERATING CURVE

P

)

P

)

P

T , AMBIENT TEMPERATURE ( C)

0

25

50 75 100 125 150 175

0

25

50

75

100

FIG.3-PULSE WAVE FORM

FIG.4-TYPICAL JUNCTION CAPACITANCE

0 1.0 2.0 3.0 4.0

t, TIME, ms

0

50

100

150

td

e-kt

tf=10 s

Peak Value

I

PPM

μ

Half Value-I

PPM

2

10/1000 sec Waveform

as Defined by R.E.A.

T =25 C

Pulse Width (td) is defined

as the point where the Peak

Current Deacys to 50% of Ipp

A

1.0 2.0 5.0 10 20 50 100 200

V(BR), BREAKDOWN VOLTAGE, VOLTS

100

200

500

10

20

50

1,000

2,000

5,000

10,000

Measured at

Stand-Off

Voltage(V

)

MW

Measued at

Zero Bias

T =25 C

f=1.0MHz

Vsig=50mVp-p

J

FIG.5-MAXIMUM NON-REPETITIVE PEAK

FORWARD SURGE CURRENT

1 5 10 20 50 100

NUMBER OF CYCLES AT 60Hz

10

20

40

60

80

100

I

,

F

T =T max

8.3ms Single Half Sine-wave

JEDEC Method

J

J

5.0mm COPPER PAD AREAS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SMAJ40A-TR | Quad 2-Input Exclusive-OR Gates 14-SOIC -55 to 125 |

| SMAJ40CA-TR | Quad 2-Input NAND Gates 14-PDIP -55 to 125 |

| SMAJ30A-TR | Quad 2-Input NOR Gates 14-PDIP -55 to 125 |

| SMAJ20A-TR | 3-Line to 8-Line Inverting Decoders/Demultiplexers 16-PDIP -55 to 125 |

| SMAJ43A-TR | TRANSILTM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SMAJ50A13 | 制造商:Diodes Incorporated 功能描述: |

| SMAJ50A13F | 制造商:Diodes Incorporated 功能描述: |

| SMAJ50ALFTR | 制造商:LITTLEFUSE 功能描述:SHIPS IN 24 HOURS GREEN |

| SMAJ50A-TR | 制造商:STMicroelectronics 功能描述:TVS DIODE, 400W, 5V, DO-214AC; Power Dissipation Pd:400W; Clamping Voltage Vc Max:9.2V; Diode Case Style:DO-214AC; No. of Pins:2; Breakdown Voltage Range:6.74V; External Depth:5.6mm; External Width:2.9mm; Leaded Process Compatible:No;RoHS Compliant: Yes |

| SMAJ50CA | 制造商:Vishay Intertechnologies 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。