- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374607 > S-24C01AFJA-11 (Seiko Instruments Inc.) The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each PDF資料下載

參數(shù)資料

| 型號: | S-24C01AFJA-11 |

| 廠商: | Seiko Instruments Inc. |

| 元件分類: | DRAM |

| 英文描述: | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| 中文描述: | 該CAT24FC02是一個2 KB的EEPROM的國內256個8位每字舉辦的串行CMOS |

| 文件頁數(shù): | 11/23頁 |

| 文件大小: | 278K |

| 代理商: | S-24C01AFJA-11 |

CMOS 2-WIRE SERIAL EEPROM

Rev. 2.2

_30

S-24C01A/02A/04A

Seiko Instruments Inc.

11

7.

Read

7.1

Current Address Read

The EEPROM is capable of storing the last accessed memory address during both writing and

reading. The memory address is stored as long as the power voltage is more than the retention

voltage V

AH

.

Accordingly, when the master device recognizes the position of the address pointer inside the

EEPROM, data can be read from the memory address of the current address pointer without

assigning a word address. This is called "Current Address Read."

"Current Address Read" is explained for when the address counter inside the EEPROM is an "n"

address.

When the EEPROM receives a 7-bit length device address and a 1-bit read/write instruction code

"1," following the start condition signal, it outputs the acknowledgment signal. However, in the S-

24C04A, page address P0 becomes invalid, and the memory address of the current address pointer

becomes valid.

Next, 8-bit length data at an "n" address is output from the EEPROM, in synchronization with the

SCL clock.

The address counter is incremented at the falling edge of the SCL clock by which the 8th bit of data

is output, and the address counter goes to address n+1.

The master device does not output the acknowledgment signal and transmits the stop condition

signal to finish reading.

For recognition of the address pointer inside the EEPROM, take into consideration the following:

The memory address counter inside the EEPROM is automatically incremented for every falling

edge of the SCL clock by which the 8th bit of data is output during the time of reading. During the

time of writing, upper bits of the memory address (upper 5 bits of the word address in the S-24C01A

and S-24C02A; upper 4 bits of the word address and page address P0 in the S-24C04A) are left

unchanged and are not incremented.

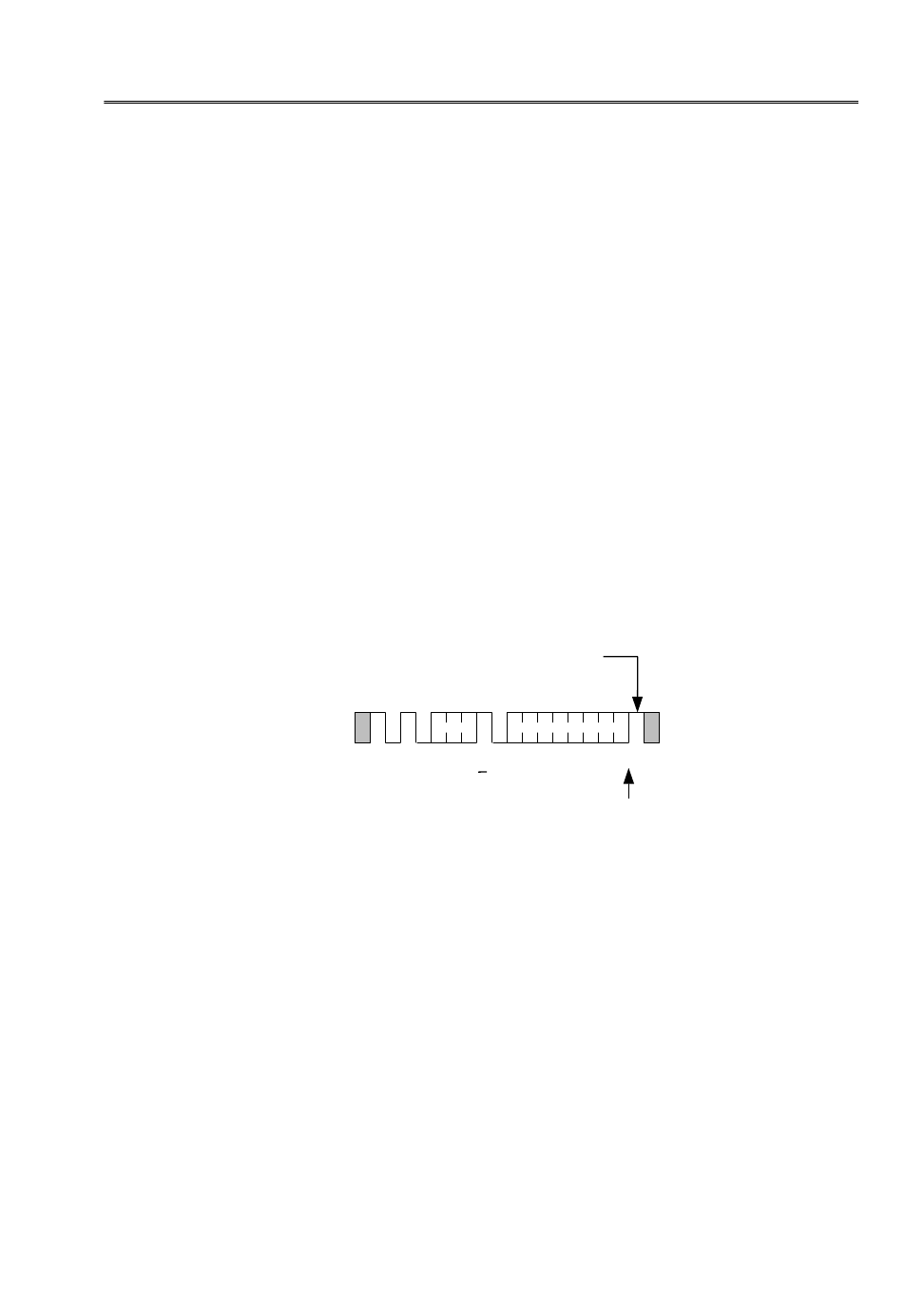

Figure 12

Current Address Read

S

T

A

R

T

1 0

1

0

R

E

A

D

S

T

O

P

DEVICE

ADDRESS

R

/

W

M

S

B

SDA LINE

ADR INC

A2 A1 A0

D7 D6 D5 D4 D3 D2 D1 D0

A

C

K

L

S

B

1

DATA

NO ACK from

Master

Device

(A0 is P0 in the S-24C04A)

相關PDF資料 |

PDF描述 |

|---|---|

| S-24C01AFJA-11-1A | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| S-24C01AFJA-11-S | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| S-24C01AFJA-TB11 | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| S-24C01AFJA-TB11-1A | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| S-24C01AFJA-TB11-S | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| S-24C01AFJA-11-1A | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS 2-WIRE SERIAL EEPROM |

| S-24C01AFJA-11-S | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS 2-WIRE SERIAL EEPROM |

| S-24C01AFJA-TB-01 | 制造商:Seiko Instruments Inc (SII) 功能描述: |

| S-24C01AFJA-TB11 | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS 2-WIRE SERIAL EEPROM |

| S-24C01AFJA-TB11-1A | 制造商:SII 制造商全稱:Seiko Instruments Inc 功能描述:CMOS 2-WIRE SERIAL EEPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復。