- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299866 > RD74LVC125BFPEL LVC/LCX/Z SERIES, QUAD 1-BIT DRIVER, TRUE OUTPUT, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | RD74LVC125BFPEL |

| 元件分類: | 總線收發(fā)器 |

| 英文描述: | LVC/LCX/Z SERIES, QUAD 1-BIT DRIVER, TRUE OUTPUT, PDSO14 |

| 封裝: | SOP-14 |

| 文件頁數(shù): | 5/9頁 |

| 文件大小: | 105K |

| 代理商: | RD74LVC125BFPEL |

RD74LVC125B

Rev.2.00 Dec. 10, 2004 page 5 of 8

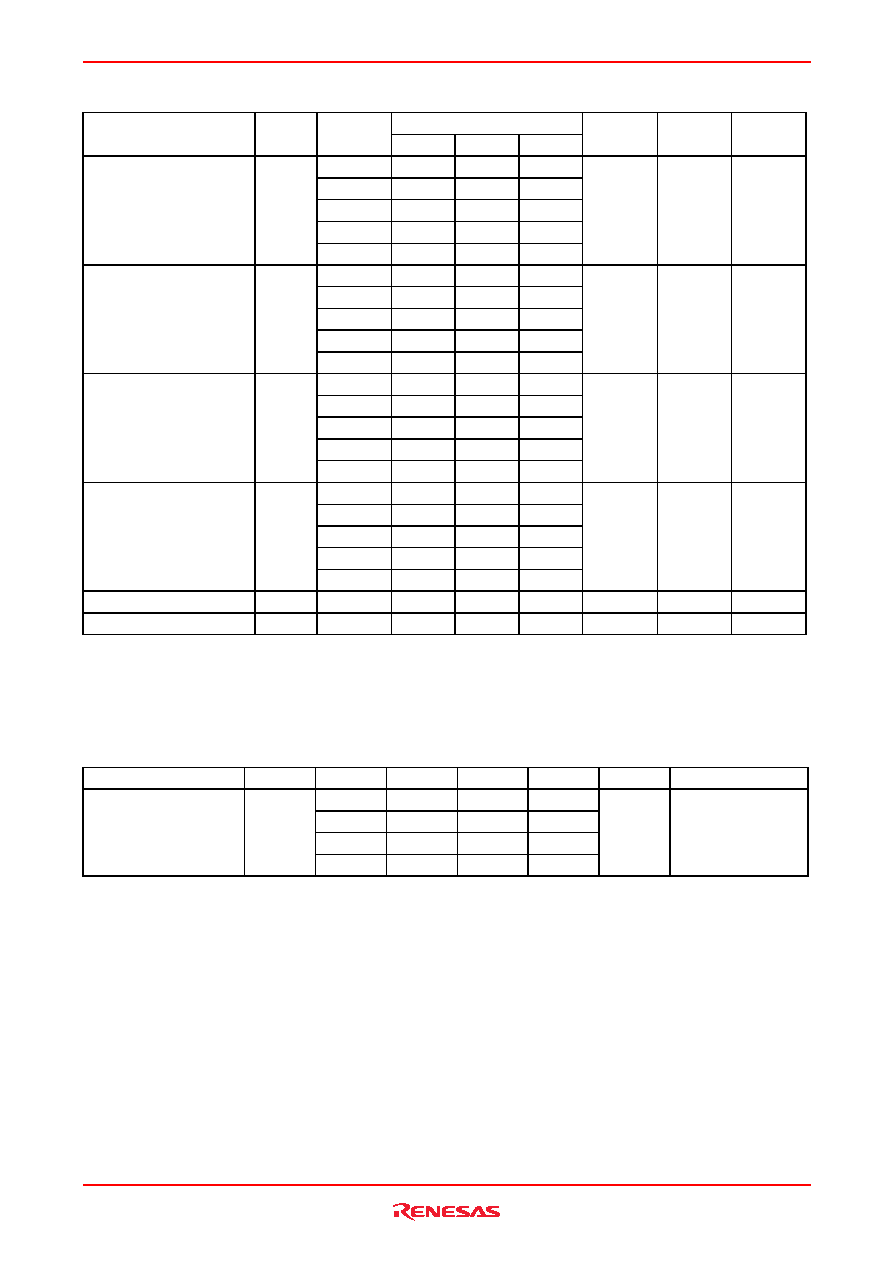

Switching Characteristics

Ta = –40 to 85°C

Item

Symbol

VCC (V)

Min

Typ

Max

Unit

From

(Input)

To

(Output)

1.8±0.15

1.0

—

12.3

2.5±0.2

1.0

—

6.3

2.7

1.0

—

5.5

3.3±0.3

1.0

—

4.8

Propagation delay time

tPLH

tPHL

5.0±0.5

1.0

—

3.8

ns

A

Y

1.8±0.15

1.0

—

14.3

2.5±0.2

1.0

—

7.4

2.7

1.0

—

6.6

3.3±0.3

1.0

—

5.4

Output enable time

tZH

tZL

5.0±0.5

1.0

—

4.4

ns

OE

Y

1.8±0.15

1.0

—

11.1

2.5±0.2

1.0

—

5.6

2.7

1.0

—

5.0

3.3±0.3

1.0

—

4.6

Output disable time

tHZ

tLZ

5.0±0.5

1.0

—

3.6

ns

OE

Y

1.8±0.15

—

2.5±0.2

—

2.7

—

3.3±0.3

—

1.0

Between output pins skew

*1 t

OSLH

tOSHL

5.0±0.5

—

1.0

ns

Input capacitance

CIN

3.3

—

4.0

—

pF

Output capacitance

CO

3.3

—

7.0

—

pF

Note:

1. This parameter is characterized but not tested.

tosLH = | tPLHm - tPLHn|, tosHL = | tPHLm - tPHLn|

Operating Characteristics

Ta = 25°C

Item

Symbol

VCC (V)

Min

Typ

Max

Unit

Test conditions

1.8

—

21

—

2.5

—

22

—

3.3

—

23

—

Power dissipation

capacitance

CPD

5.0

—

27

—

pF

f = 10 MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RD74LVC139BFPEL | LVC/LCX/Z SERIES, OTHER DECODER/DRIVER, INVERTED OUTPUT, PDSO16 |

| RD74LVC14BTELL | LVC/LCX/Z SERIES, HEX 1-INPUT INVERT GATE, PDSO14 |

| RD74LVC1G07WPE | LVC/LCX/Z SERIES, 1-INPUT NON-INVERT GATE, PBGA5 |

| RD74LVC2G02WPE | LVC/LCX/Z SERIES, DUAL 2-INPUT NOR GATE, PBGA8 |

| RD74LVC540BFPEL | LVC/LCX/Z SERIES, 8-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RD74LVC125BTELL | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Quad. Bus Buffer Gates with 3-state Outputs |

| RD74LVC126B | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Quad. Bus Buffer Gates with 3-state Outputs |

| RD74LVC126BFPEL | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Quad. Bus Buffer Gates with 3-state Outputs |

| RD74LVC126BTELL | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:Quad. Bus Buffer Gates with 3-state Outputs |

| RD74LVC138B | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:3-to-8-line Decoder / Demultiplexer |

發(fā)布緊急采購,3分鐘左右您將得到回復。