- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374575 > RD28F3204W30T70 (INTEL CORP) 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) PDF資料下載

參數(shù)資料

| 型號: | RD28F3204W30T70 |

| 廠商: | INTEL CORP |

| 元件分類: | 存儲器 |

| 英文描述: | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| 中文描述: | SPECIALTY MEMORY CIRCUIT, PBGA80 |

| 封裝: | 14 X 8 MM, 0.80 MM PITCH, STACK, CSP-80 |

| 文件頁數(shù): | 19/82頁 |

| 文件大小: | 749K |

| 代理商: | RD28F3204W30T70 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

28F6408W30, 28F3204W30, 28F320W30, 28F640W30

Preliminary

13

Burst mode is

not

the default mode after power-up or a device reset. To perform a burst-mode read,

the configuration register must be set. To set the configuration register, refer to

Section 4.2,

“

Set

Configuration Register (CR)

”

on page 13

. After setting the configuration register, if the first device

operation is a burst-mode read, it is not necessary to execute the Read Array command before

accessing the flash memory. However, to perform a flash read at any other time, it is necessary to

execute the Read Array command before accessing the flash memory array.

Burst mode is permitted in all blocks, across all partition boundaries and operates independently of

V

PP.

A single-word burst-mode read

cannot

be used to access register information. In burst mode,

the address is latched by either the rising edge of ADV# or the rising edge of CLK with ADV# low,

whichever occurs first.

Upon completion of reading the array, the device automatically enters an Automatic Power Savings

(APS) mode. APS mode consumes power comparable to standby mode.

4.2

Set Configuration Register (CR)

The configuration register is 16 bits wide. This register is used to configure the burst mode

parameters. Therefore, if using page mode, it is not necessary to set this register.

To set the configuration register, execute the Set Configuration Register command. The 16 bits of

data used by this command must be placed on address lines A

15

–

0

. All other address lines must be

held low (V

IL

).

After setting the configuration register, if the first device operation is a flash burst-mode read, it is

not necessary to execute the Read Array command before accessing the flash memory. However, to

perform a burst-mode read at any other time, it is necessary to execute the Read Array command

before accessing the flash memory.

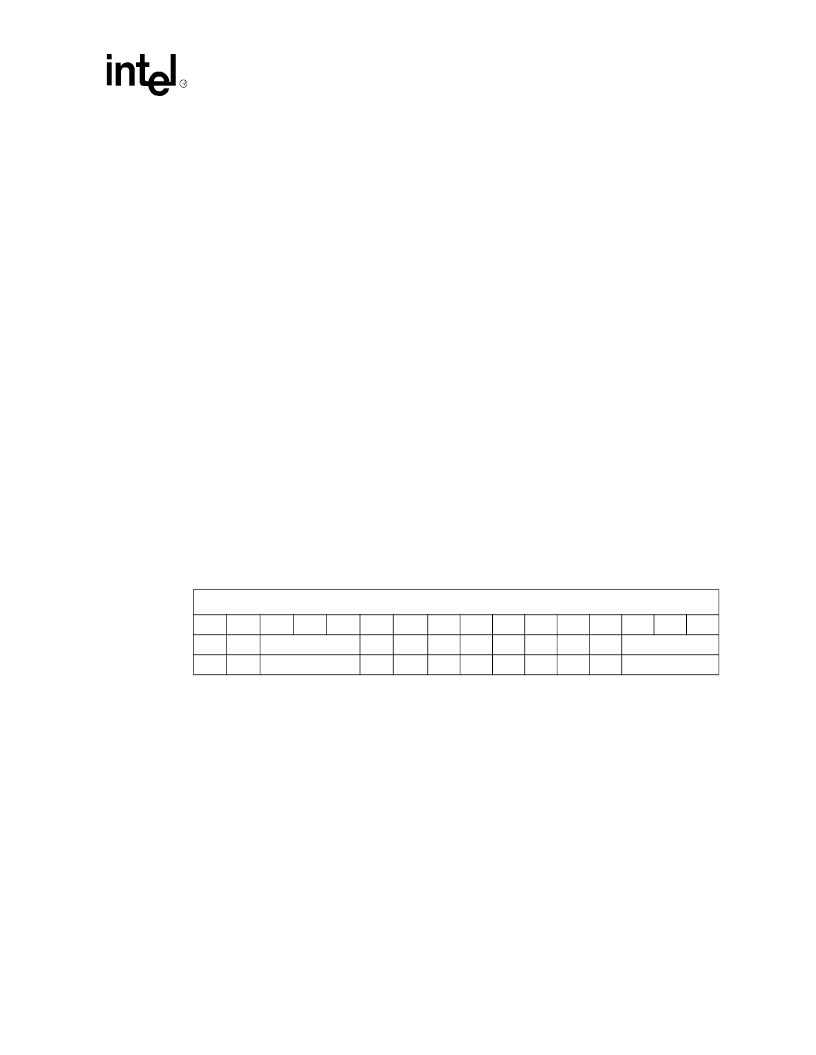

NOTES:

1.

‘

R

’

bits are reserved bits. These bits and all other address lines must be set low.

2. On power-up or return from reset, all bits are set to

“

1.

”

Table 6. Configuration Register Bits

Configuration Register Bits

2

A

15

A

14

R

1

A

13

A

12

A

11

A

10

A

9

A

8

A

7

A

6

A

5

R

1

A

4

R

1

A

3

A

2

A

1

A

0

RM

LC

2-0

WT

DOC

WC

BS

CC

BW

BL

2-0

0

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RD28F3204W30T85 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| RD28F6408W30B70 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| RD28F6408W30B85 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| RD28F6408W30T70 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| RD28F6408W30T85 | 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RD28F3204W30T85 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM (W30) |

| RD28F3208C3B70 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 VOLT INTEL Advanced+ Boot Block Flash Memory (C3) Stacked-Chip ScalPackage Familye |

| RD28F3208C3B90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 VOLT INTEL Advanced+ Boot Block Flash Memory (C3) Stacked-Chip ScalPackage Familye |

| RD28F3208C3T70 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 VOLT INTEL Advanced+ Boot Block Flash Memory (C3) Stacked-Chip ScalPackage Familye |

| RD28F3208C3T90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 VOLT INTEL Advanced+ Boot Block Flash Memory (C3) Stacked-Chip ScalPackage Familye |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。