- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361005 > PLSI2032-135LT Electrically-Erasable Complex PLD PDF資料下載

參數(shù)資料

| 型號(hào): | PLSI2032-135LT |

| 英文描述: | Electrically-Erasable Complex PLD |

| 中文描述: | 電可擦除復(fù)雜可編程邏輯器件 |

| 文件頁(yè)數(shù): | 7/12頁(yè) |

| 文件大小: | 120K |

| 代理商: | PLSI2032-135LT |

Specifications

ispLSI 1048

7

USEispLS 1048EAFORNEW

COMMERCAL&INDUSTRAL

DESGNS

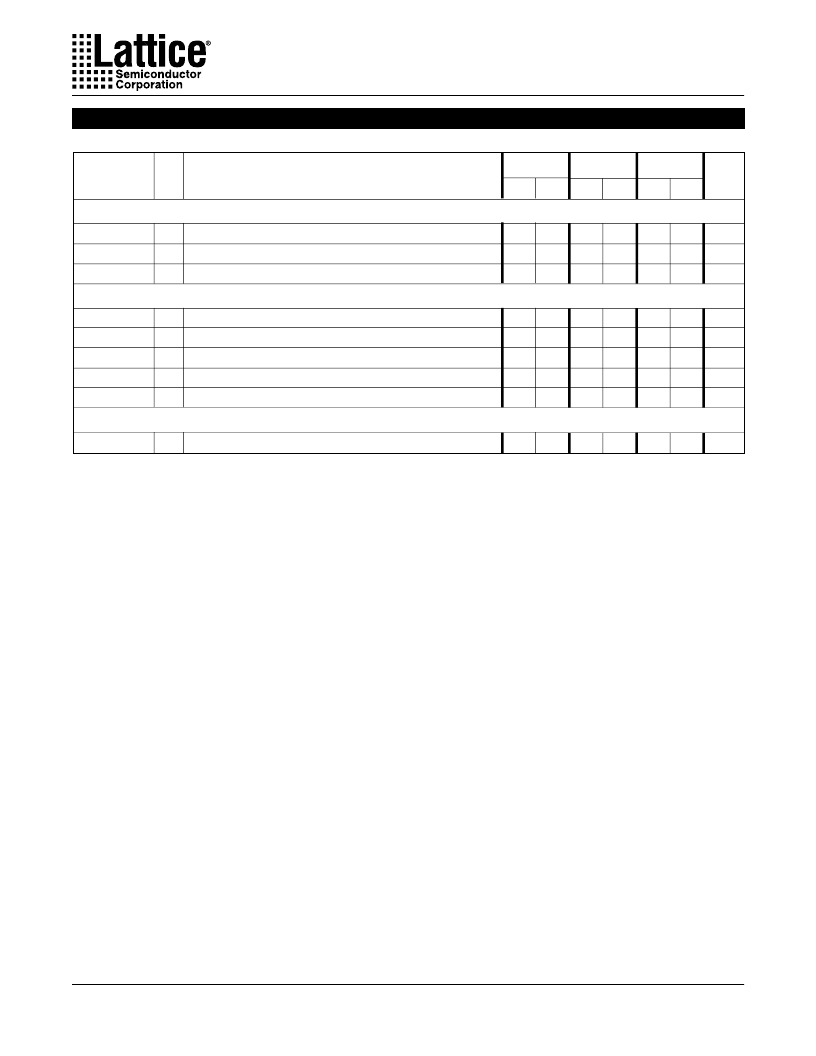

Internal Timing Parameters

1

ns

ns

ns

ns

ns

ns

ns

ns

ns

–

–

–

6.7

5.3

1.3

5.3

1.3

–

4.0

6.7

6.7

6.7

8.0

6.6

8.0

6.6

10.6

Outputs

t

ob

t

oen

t

odis

Clocks

t

gy0

t

gy1/2

t

gcp

t

ioy2/3

t

iocp

Global Reset

t

gr

47

49

50

51

52

53

54

55

Output Buffer Delay

I/O Cell OE to Output Disabled

Clock Delay, Y0 to Global GLB Clock Line (Ref. clock)

Clock Delay, Y1 or Y2 to Global GLB Clock Line

Clock Delay, Clock GLB to Global GLB Clock Line

Clock Delay, Y2 or Y3 to I/O Cell Global Clock Line

Clock Delay, Clock GLB to I/O Cell Global Clock Line

Global Reset to GLB and I/O Registers

MIN. MAX.

DESCRIPTION

PARAMETER

UNITS

-50

#

2

–

–

5.0

4.0

1.0

4.0

1.0

–

3.0

5.0

5.0

6.0

5.0

6.0

5.0

8.0

MIN. MAX.

-70

1. Internal Timing Parameters are not tested and are for reference only.

2. Refer to Timing Model in this data sheet for further details.

–

–

4.2

3.3

0.8

3.3

0.8

–

2.5

4.2

4.2

5.0

4.2

5.0

4.2

9.2

MIN. MAX.

-80

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PLSI2032-150LT | High Speed Single/Dual N-Channel MOSFET Drivers; Package: SO; No of Pins: 8; Temperature Range: 0°C to +70°C |

| PLSI2032-80LT | Electrically-Erasable Complex PLD |

| PLSI1016-60LT | Electrically-Erasable Complex PLD |

| PLSI1016-80LT | Electrically-Erasable Complex PLD |

| PLSI1016-90LT | Low Glitch 16-Bit Voltage Output DAC; Package: PDIP; No of Pins: 16; Temperature Range: 0°C to +70°C |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PLSI2032-135LT44 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| PLSI2032-150LJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| PLSI2032-150LT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| PLSI2032-150LT44 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

| PLSI2032-180LJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Electrically-Erasable Complex PLD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。