- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1960 > PI2EQX4432DZDEX (Pericom)IC PCI-E REPEATER/EQUALR 48TQFN PDF資料下載

參數(shù)資料

| 型號(hào): | PI2EQX4432DZDEX |

| 廠商: | Pericom |

| 文件頁數(shù): | 2/6頁 |

| 文件大小: | 0K |

| 描述: | IC PCI-E REPEATER/EQUALR 48TQFN |

| 標(biāo)準(zhǔn)包裝: | 3,000 |

| 系列: | * |

2

PS8888A

04/26/07

PI2EQX4432D

2.5Gbps x2 Lane PCI Express Repeater / Equalizer

with Signal Detect and Flow-through Pinout

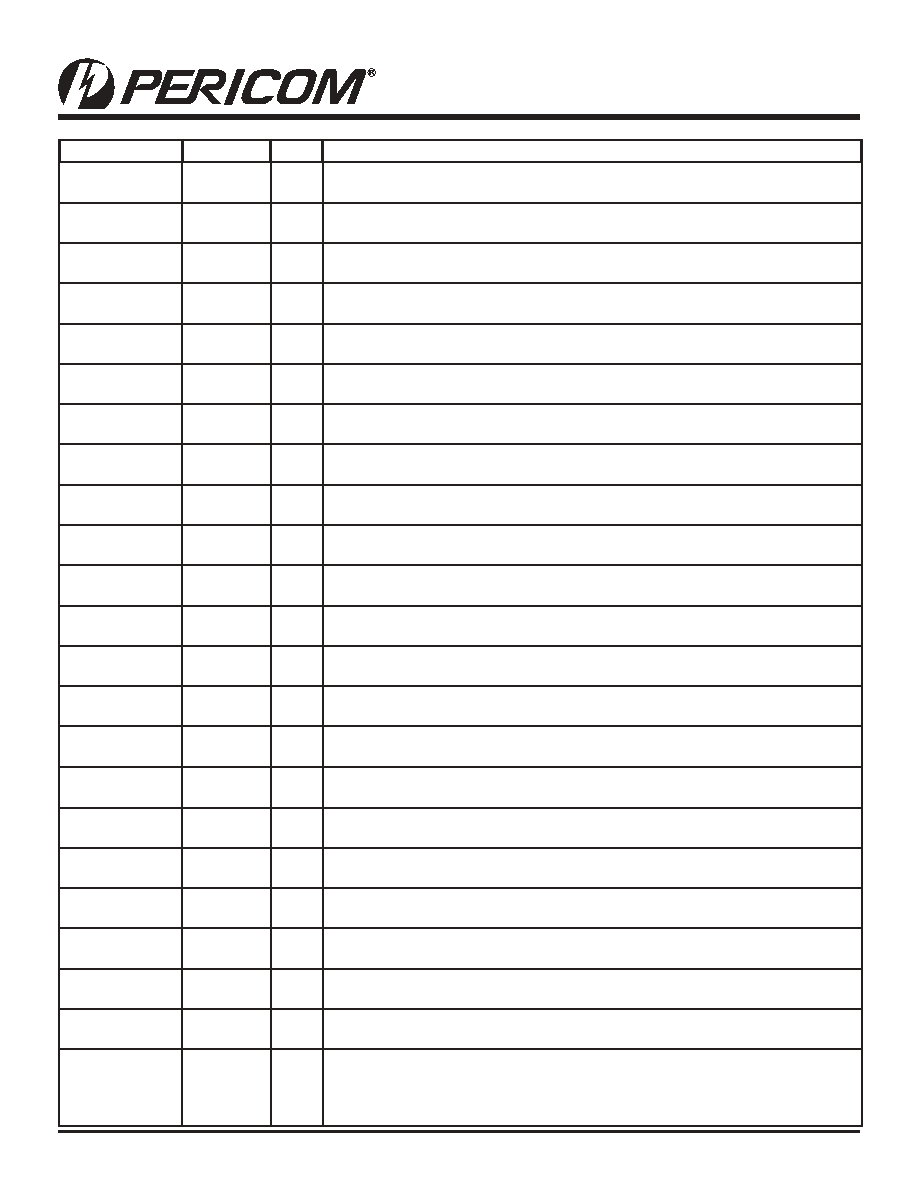

Pin Description

Pin #

Pin Name

I/O

Description

1

AI+

I

Positive CML Input Channel A with internal 50 Ohm pull down during normal opera-

tion (EN_A = 1). When EN_A = 0, this pin is a high-impedance.

2

AI-

I

Negative CML Input Channel A with internal 50 Ohm pull down during normal op-

eration (EN_A = 1). When EN_A =0, this pin is a high-impedance.

36

AO+

O

Positive CML Output Channel A internal 50 Ohm pull up during normal operation and

2KΩ pull up otherwise.

35

AO-

O

Negative CML Output Channel A with internal 50 Ohm pull up during normal opera-

tion and 2K-ohm pull up otherwise.

33

BI+

Posite CML Input Channel B with internal 50 Ohm pull down during normal opera-

tion (EN_B = 1). When EN_B = 0, this pin is a high-impedance.

32

BI-

I

Negative CML Input Channel B with internal 50 Ohm pull down during normal opera-

tion (EN_B = 1). When EN_B = 0, this pin is a high-impedance.

4

BO+

O

Positive CML Output Channel B with internal 50 Ohm pull up during normal opera-

tion and 2k–Ohm pull up otherwise.

5

BO-

O

Negative CMLOutput Channel B with internal 50 Ohm pull up during normal opera-

tion and 2k–Ohm pull up otherwise.

7

CI+

I

Positive CML Input Channel C with internal 50 Ohm pull down during normal opera-

tion (EN_C = 1). When EN_C = 0, this pin is a high-impedance.

8

CI-

I

Negative CML Input Channel C with internal 50 Ohm pull down during normal opera-

tion (EN_C = 1). When EN_C = 0, this pin is a high-impedance.

30

CO+

O

Positive CMLOutput Channel C with internal 50 Ohm pull up during normal opera-

tion and 2K-ohm pull up otherwise.

29

CO-

O

Negative CMLOutput Channel C with internal 50 Ohm pull up during normal opera-

tion and 2k–Ohm pull up otherwise.

27

DI+

I

Positive CML Input Channel D with internal 50 Ohm pull down during normal opera-

tion (EN_D = 1). When EN_D = 0, this pin is a high-impedance.

26

DI-

I

Negative CML Input Channel D with internal 50 Ohm pull down during normal op-

eration (EN_D = 1). When EN_D = 0, this pin is a high-impedance.

10

DO+

O

Positive CML Output Channel D with internal 50 Ohm pull up during normal opera-

tion and 2k–Ohm pull up otherwise.

11

DO-

O

Negative CML Output Channel D with internal 50

Ω pull up during normal operation

and 2k–Ohm pull up otherwise.

41, 40, 39, 38

EN_[A, B,

C, D]

I

EN_[A:D] is a channel enable pin with internal 50k–Ohm pull-up resistor. ALVCMOS

high provides normal operation. ALVCMOS low selects a low power down mode.

43, 42, 20, 21

SEL–DE_

[A:D]

I

Output De–Emphasis conguration input for channels A, B, C and D, with internal

50k–Ohm pull up.Refer to table for modes.

47, 46, 16, 17

SEL–EQ_

[A:D]

I

Equalizer conguration input for channels A, B, C and D, with internal 50k–Ohm

pull-up. Refer to table for modes.

45, 44, 18, 19

SEL–OL_

[A:D]

I

Output Level conguration input for channels A, B, C, and D, with internal 50k–Ohm

pull–up. Refer to table for modes.

14, 15

CLK+,

CLK–

I

Differential input reference clock, typically 100MHz

22, 23

CLKO,

CLKO–

O

Differential reference clock output

13

EN_CLK

I

Enable Clock input with 50K–Ohm pull-up. When EN_CLK is LVCMOS high level,

the clock output operates normally. When EN_CLK = low, the clock outputs are

turned off for power savings. A clock is not required bt the data channels for opera-

tion.

07-0106

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI2EQX4951SLZDE | IC SATA2 REDRIVER 20TQFN |

| PI2EQX5804CNJE | IC PCI-E REDRIVER 100LBGA |

| PI2EQX5864CZFE | IC PCI-E REDRIVER 56TQFN |

| PI2EQX5904NJE | IC PCIE 2.0 REDRIVER 100LBGA |

| PI2EQX5964ZFE | IC PCIE 2.0 REDRIVER 56TQFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI2EQX4951SLZDE | 功能描述:緩沖器和線路驅(qū)動(dòng)器 SATA REDRIVER 1 PORT RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| PI2EQX4951SLZDEX | 功能描述:緩沖器和線路驅(qū)動(dòng)器 1.5V 1prt SATA2 I/m ReDrvr w/ A/D Config RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| PI2EQX5804C | 制造商:PERICOM 制造商全稱:Pericom Semiconductor Corporation 功能描述:5.0Gbps 4-Lane PCIe?? 2.0 ReDrivera?¢ with Equalization & Emphasis |

| PI2EQX5804CNJE | 功能描述:緩沖器和線路驅(qū)動(dòng)器 PCI-Express Gen-2 5.0Gbps RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| PI2EQX5804CNJEX | 功能描述:緩沖器和線路驅(qū)動(dòng)器 PCI-Express Gen-2 5.0Gbps RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。