- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299640 > PDSP16488AMAACBR (ZARLINK SEMICONDUCTOR INC) 16-BIT, DSP-CONVOLVER, CPGA84 PDF資料下載

參數(shù)資料

| 型號(hào): | PDSP16488AMAACBR |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字信號(hào)處理外設(shè) |

| 英文描述: | 16-BIT, DSP-CONVOLVER, CPGA84 |

| 封裝: | PGA-84 |

| 文件頁(yè)數(shù): | 16/30頁(yè) |

| 文件大小: | 290K |

| 代理商: | PDSP16488AMAACBR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)

PDSP16488A MA

23

EPROM

DELAYED

SYNC

CLOCK

BIN

OVERFLOW

DATA OUT

SYNC

O/C

MSB

O/C

16 BIT

PIXEL

DATA

LSB

RESET

O/P ENABLE

PC0

X15

X14:8

X7:0

IP7:0

HRES

BYPASS

L7:0

CE

D15:0

PROG

PDSP

16488

8X4

WINDOW

GND

RES

PC1

CS0

DS

SNG

MST

R/W

GND

DELOP

O/C

GND

CS1

PC0

X15

X14:8

X7:0

IP7:0

HRES

BYPASS

L7:0

CE

D15:0

PROG

CLOCK

PDSP

16488

8X4

WINDOW

RES

PC1

DS

SNG

MST

R/W

OEN

O/C

GND

O/C

BIN

OV

MSB

OEN

GND

O/C

DELAYED

SYNC

CLOCK

BIN

OVERFLOW

DATA OUT

SYNC

16 BIT

PIXEL

DATA

RESET

O/P ENABLE

PC0

X15

X14:8

X7:0

IP7:0

HRES

BYPASS

L7:0

CE

D15:0

PROG

CLOCK

PDSP

16488

8X4

WINDOW

O/C

RES

PC1

SNG

MST

R/W

GND

DELOP

O/C

PC0

X15

X14:8

X7:0

IP7:0

HRES

BYPASS

L7:0

CE

D15:0

PROG

CLOCK

PDSP

16488

8X4

WINDOW

RES

PC1

SNG

MST

R/W

OEN

O/C

BIN

OV

R/W

ADDR

DATA

STROBE

HOST CPU

ADDRESS

DECODE

DS

ODD

FIELD

DELAY

REPLY

READ

REG

OEN

GND

O/C

MSB

LSB

D7;0

CLOCK

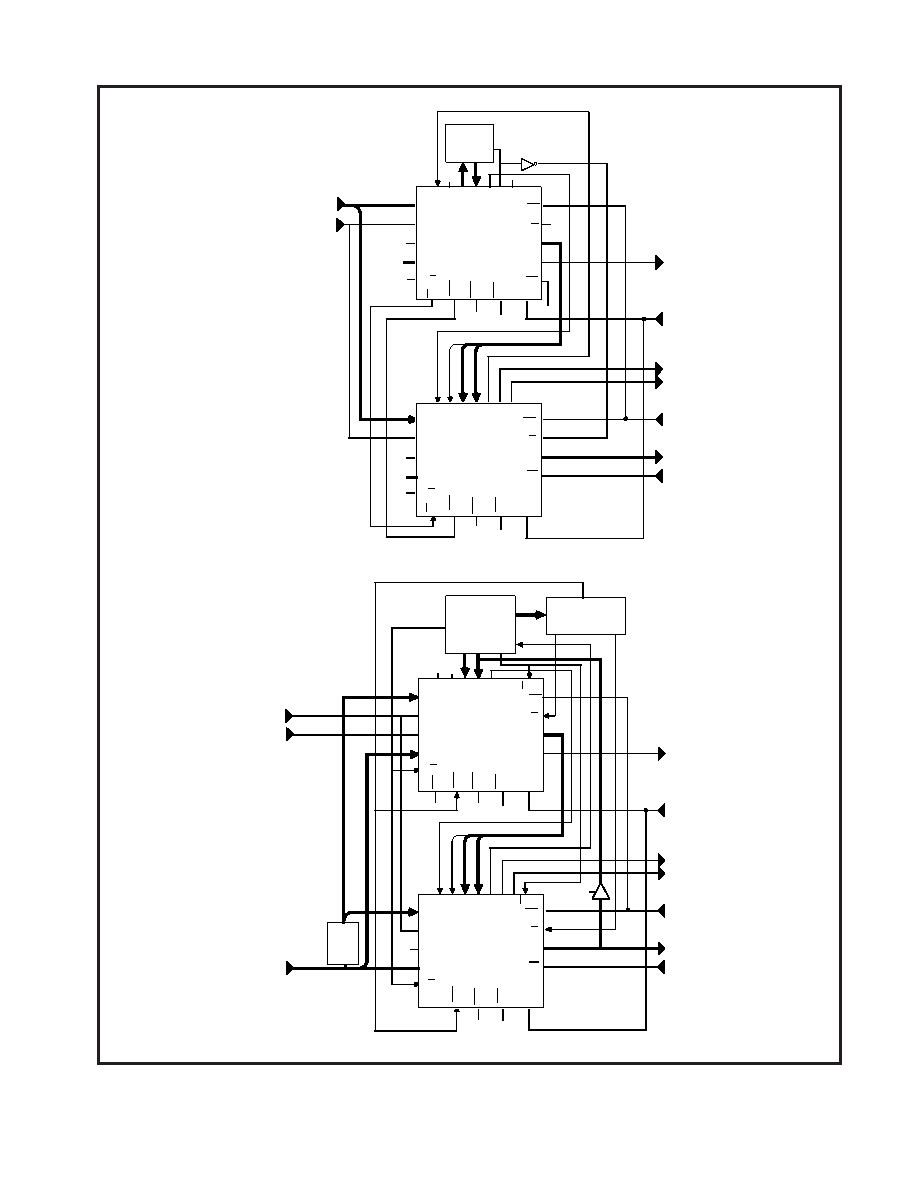

Figure 13. Dual Device 16 Bit Systems.

VCC

PDSP

16488A

8X4

WINDOW

PDSP

16488A

8X4

WINDOW

PDSP

16488A

8X4

WINDOW

PDSP

16488A

8X4

WINDOW

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PE-0402CD2N2KTT | 1 ELEMENT, 0.0022 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| PE-0402CD6N2JTT | 1 ELEMENT, 0.0062 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| PE-0805CX470KBT | 1 ELEMENT, 0.047 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| PE-0805CX681KBT | 1 ELEMENT, 0.68 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

| PE-0805CX681JBT | 1 ELEMENT, 0.68 uH, CERAMIC-CORE, GENERAL PURPOSE INDUCTOR, SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDSP16488AMAGCPR | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Single Chip 2D Convolver with Integral Line Delays |

| PDSP16488B0 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Single Chip 2D Convolver with Integral Line Delays |

| PDSP16488B0AC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Convolver |

| PDSP16488B0GC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Convolver |

| PDSP16488C0 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Single Chip 2D Convolver with Integral Line Delays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。