- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385710 > PDSP16318GC1R (Mitel Networks Corporation) CAT5E PATCH CORD SNAGLESS, GREEN 100FT PDF資料下載

參數(shù)資料

| 型號: | PDSP16318GC1R |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CAT5E PATCH CORD SNAGLESS, GREEN 100FT |

| 中文描述: | PDSP16256GC1R |

| 文件頁數(shù): | 6/8頁 |

| 文件大?。?/td> | 88K |

| 代理商: | PDSP16318GC1R |

PDSP16318/16318A

6

Min.

100

20

20

8

2

10

8

2

2

8

5

-

-

-

-

-

Max.

-

-

-

-

-

-

-

-

-

-

30

30

30

30

110

60

Min.

50

15

15

5

2

10

5

2

2

8

5

-

-

-

-

-

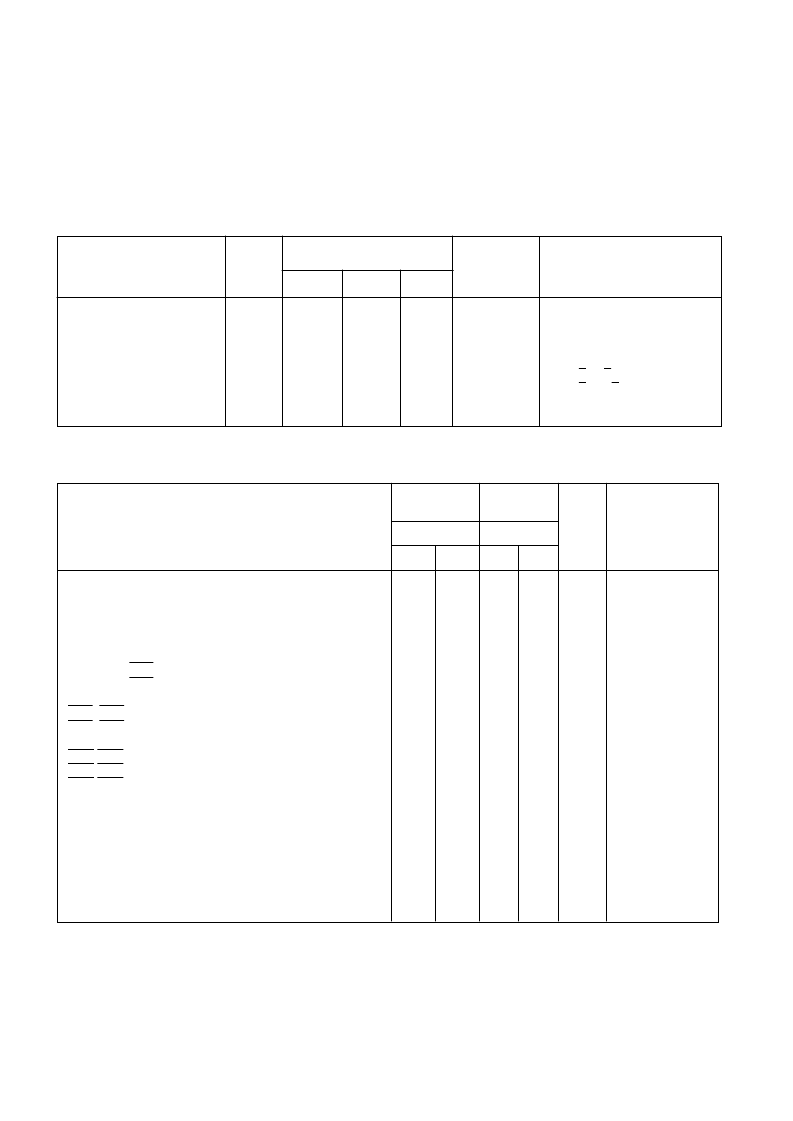

ELECTRICAL CHARACTERISTICS

Test conditions (unless otherwise stated):

T

amb

(Commercial) = 0

°

C to +70

°

C, V

CC

= 5.0V

±

5%, GND = 0V

T

amb

(Industrial) =-40

°

C to +85

°

C, V

CC

= 5.0V

±

10%, GND = 0V

T

amb

(Military) =-55

°

C to +125

°

C, V

CC

= 5.0V

±

10%, GND = 0V

STATIC CHARACTERISTICS

Value

Characteristic

Symbol

Units

Max.

Conditions

Min.

Typ.

Output high voltage

Output low voltage

Input high voltage

Input low voltage

Input leakage current

Output leakage current

Output SC current

Input capacitance

V

OH

2.4

-

3.5

-

-10

-50

20

-

-

0.4

-

0.5

+10

+50

200

-

V

V

V

V

μ

A

μ

A

mA

pF

I

OH

= 3.2mA

l

OL

=-3.2mA

V

OL

V

IH

V

IL

I

IL

l

oz

I

OS

C

IN

GND < V

IN

<V

GND <V

OUT

< V

CC

V

cc

= Max

-

-

9

Max.

-

-

-

-

-

-

-

-

-

-

40

40

40

40

70

30

Characteristic

Clock period

Clock High Time

Clock Low Time

A15:0, B15:0 setup to clock rising edge

A15:0, B15:0 hold after clock rising edge

MS, S2:0, ASI setup to clock rising edge

DEL, ASR,

CLR

setup to clock rising edge

DEL, ASR,

CLR

, MS, S2:0, ASI hold after

clock rising edge

CEA

,

CEB

setup to clock falling edge

CEA

,

CEB

hold after clock rising edge

Clock rising edge to OVR, C15:0, D15:0

OEC

/

OED

low to C15:0/D15:0 high data valid

OEC

/

OED

low to C15:0/D15:0 low data valid

OEC

/

OED

high to C15:0/D15:0 high impedance

Vcc current

Vcc current

Conditions

2 x LSTTL + 20pF

2 x LSTTL + 20pF

2 x LSTTL + 20pF

2 x LSTTL + 20pF

V

CC

= max,

TTL input levels

Outputs unloaded,

f

CLK

= max

V

CC

= max,

CMOS input levels

Outputs unloaded,

f

CLK

= max

SWITCHING CHARACTERISTICS

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

mA

mA

PDSP16318

PDSP16318A

Value

Industrial

Value

Military

NOTES

1.

2.

3.

LSTTL is equivalent to I

= 20 microamps, I

OL

= -0.4mA

Current is defined as negative into the device

CMOS input levels are defined as:

V

IL

= 0.5

V

IH

= V

DD

- 0.5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PDSP16318MC | PDSP16256GC1R |

| PDSP16318A | PDSP16256GC1R |

| PDSP16318 | Complex Accumulator(復(fù)雜累加器(由兩個獨(dú)立的20位加法器/減法器組成)) |

| PDSP16318A | Complex Accumulator(復(fù)雜累加器(由兩個獨(dú)立的20位加法器/減法器組成)) |

| PDSP16318IG | CAT5E PATCH CABLES SNAGLESS PINK 20 FT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PDSP16318IG | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:PDSP16256GC1R |

| PDSP16318LC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PDSP16318MC | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Complex Accumulator |

| PDSP16330 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Pythagoras Processor |

| PDSP16330A | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Pythagoras Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。