- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382369 > P90CL301 (NXP Semiconductors N.V.) Low voltage 16-bit microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | P90CL301 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Low voltage 16-bit microcontroller |

| 中文描述: | 低電壓16位微控制器 |

| 文件頁數(shù): | 10/92頁 |

| 文件大小: | 526K |

| 代理商: | P90CL301 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

1996 Dec 11

10

Philips Semiconductors

Preliminary specification

Low voltage 16-bit microcontroller

P90CL301BFH (C100)

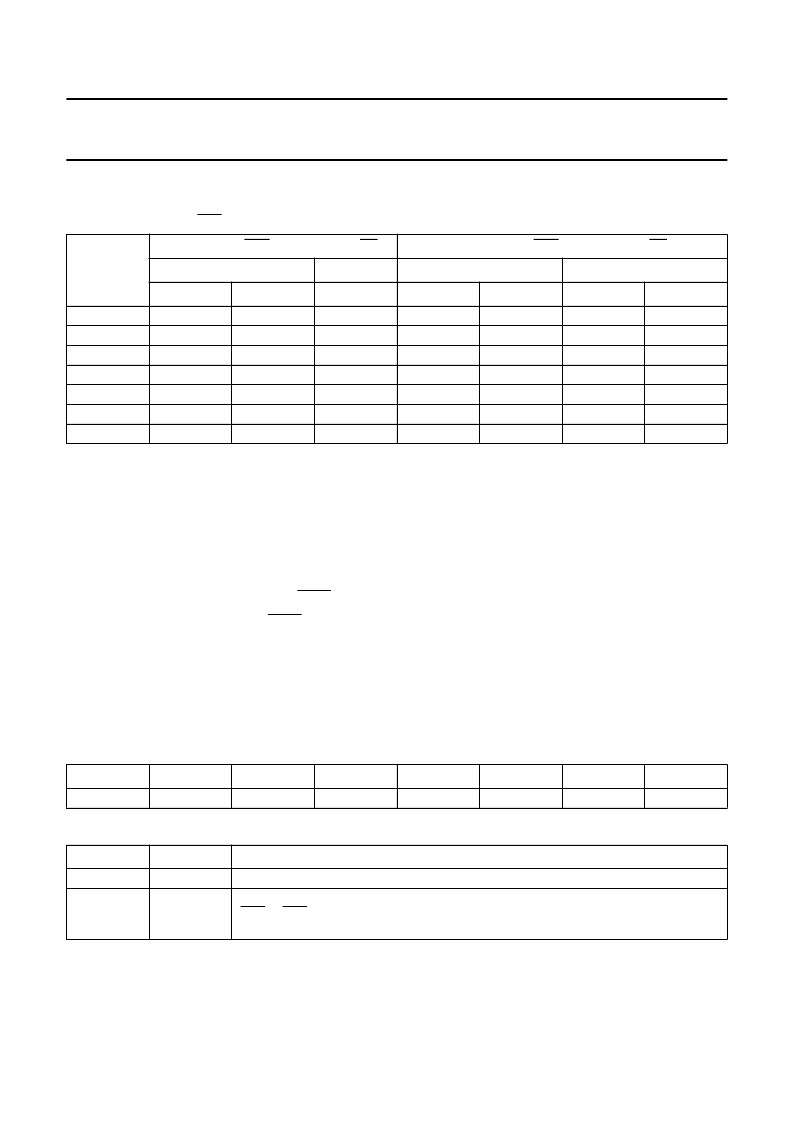

Table 9

Number of clock periods per bus cycle, dependent on the programmed length of FBC (Fast Bus Cycle bit in the

SYSCON register) and CSn (chip-select).

Number of clock periods per bus cycle

WAIT

STATES

LENGTH OF CSn = LENGTH OF AS

LENGTH OF CSn = LENGTH OF DS

FBC = 1

FBC = 0

FBC = 1

FBC = 0

READ

WRITE

R/W

READ

WRITE

READ

WRITE

0

1

2

3

4

5

6

3

4

5

6

7

8

9

4

4

5

6

7

8

9

4

4

5

6

7

8

9

3

4

5

6

7

8

9

4

5

6

7

8

9

4

4

5

6

7

8

9

4

5

6

7

8

9

10

10

6.3

Dynamic bus port sizing

The memory bus size can be selected to be 16 or 8-bit

wide depending on the ports width of external memories

and peripherals. It is possible via the register BSREG to

define for each chip-select the bus width to 16-bit or 8-bit

used for the transfer of data to or from external memory.

The 7-bit register BSREG defines the bus size associated

with each chip-select function (except for CSBT).

The bus size of the chip-select boot CSBT (CS7N) is

hardware defined by the pin BSIZE.The state of the pin

BSIZE is latched at the end of the reset sequence.

When an address generated by the CPU is identified by a

chip-select block as belonging to it’s address segment, the

corresponding bit of the register BSREG is used to define

the sequence of bus transfer in 16 or 8-bit mode. Several

chip-selects with different bus sizes should not address

the same memory segment. For each case the number of

bus cycles necessary to transfer a byte, word or long word

is a function of the bus size. For example, a word read on

a 8-bit bus will take 2 bus cycles and the high byte is read

first. The 8-bit port uses the pins D7 to D0.

See Table 11 and 12 and also Section 6.2 for more

detailed information on the programmable chip-selects

and the dynamic bus sizing.

6.3.1

B

US

S

IZE

R

EGISTER

(BSREG)

Table 10

Bus Size Register (address FFFF A811H)

Table 11

Description of BSREG bits

7

6

5

4

3

2

1

0

BS6

BS5

BS4

BS3

BS2

BS1

BS0

BIT

SYMBOL

BS6 to BS0

DESCRIPTION

7

Reserved.

Bus size for the data transfer with respect to the corresponding chip-select

(CS6 to CS0). If BSn = 0, then the bus size is in 16-bit mode; the default value after a

CPU reset. If BSn = 1, then the bus size is in 8-bit mode. Where n = 0 to 6.

6 to 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P90CL301BFH | Low voltage 16-bit microcontroller |

| P93U422-35DC | x4 SRAM |

| P93U422-35DM | x4 SRAM |

| P93U422-35DMB | x4 SRAM |

| P93U422-35LC | x4 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P90CL301BFH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low voltage 16-bit microcontroller |

| P-90-F | 制造商:Hozan Tool Industrial Co Ltd 功能描述: |

| P90PCT101PC | 制造商:PERFORMANCE/ 功能描述:90PCT101PC |

| P-910 | 制造商:Hozan Tool Industrial Co Ltd 功能描述: |

| P9-100001 | 制造商:OTTO Engineering Inc 功能描述:P9-111122 EX H20 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。