- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384806 > OXFW900-TQ-A (Electronic Theatre Controls, Inc.) IEEE1394 to ATA/ATAPI Native Bridge PDF資料下載

參數(shù)資料

| 型號(hào): | OXFW900-TQ-A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | IEEE1394 to ATA/ATAPI Native Bridge |

| 中文描述: | IEEE1394連接到ATA / ATAPI的母語橋 |

| 文件頁數(shù): | 6/30頁 |

| 文件大小: | 187K |

| 代理商: | OXFW900-TQ-A |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁

Data Sheet Revision 1.0

Page 6

OXFW900

OXFORD SEMICONDUCTOR LTD.

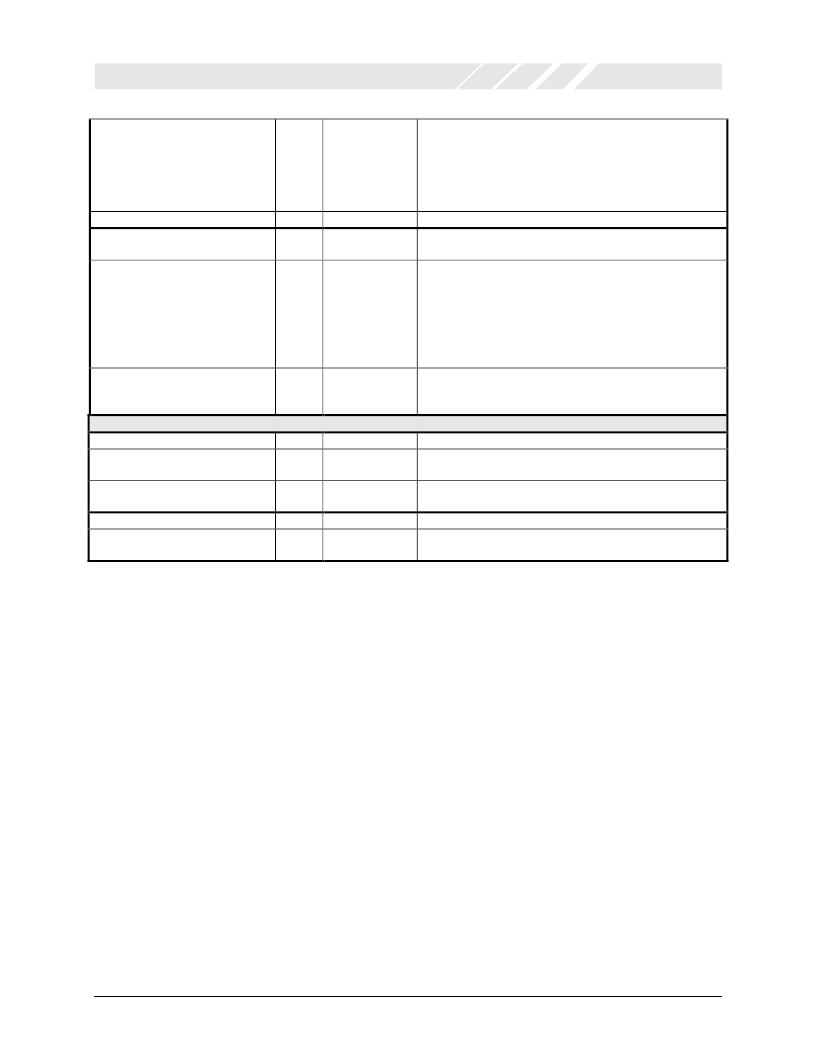

56

I

CKIN

Direct clock input. Used in conjunction with an external

crystal oscillator of 24.576MHz. If a crystal is connected to

XTLI and XTLO this input must be tied low for the OXFW900

to operate. Mark space ratio of crystal oscillator must be

45:55 or better. IMPORTANT – Please refer to Application

Notes regarding clocking

Global reset for the OXFW900. Active Low.

Clock output. 24.576 MHz clock output. IMPORTANT –

Please refer to Application Notes regarding clocking

This input is used to allow the OXFW900 to reprograma

flash which has been loaded with a bad program A bad

programis defined as one that does not have the correct

interlocking mechanismfor reprogrammng flash. This pin

forces the ARMwatchdog timer to trigger thus allowing the

flash to be reprogrammed over the 1394 bus as if the flash

were blank.

‘11’ = NORMAL OPERATION. These pins have internal

pullup resistors and must be left unconnected. Other settings

are for foundry test purposes only.

23

113

IU

T_O

RESET#

CKOUT

123

IU

FORCE#

124, 125

IU

TEST[1:0]

Power and ground

2

28, 47, 94, 114

17, 24, 59, 84, 88, 121

3V3

3V3

3.3V AC VDD

3.3V DC VDD

Supplies power to output buffers in switching (AC) state

Power supply. Supplies power to core logic, input buffers

and output buffers in steady state

Supplies 5V reference bias to all 5V tolerant I/O. All four

MUST be connected to 5V rail.

Supplies GND to output buffers in switching (AC) state

Ground (0 volts). Supplies GND to core logic, input buffers

and output buffers in steady state

9, 38, 76, 112

5V

5V BIAS VDD

8, 27, 46, 67, 75, 93, 106

16, 22, 39, 55, 68, 83, 87, 107, 119

G

G

AC GND

DC GND

Table 1: Pin Descriptions

Note 1: Direction key:

I

Input

IU

Input with internal pull-up

ID

Input with external pull-down

O

Output

I/O

Bi-directional

T_I

5V tolerant input

Note 2: Power & Ground

There are two GND and three VDD rails internally. One set of rails supply power and ground to output buffers while in switching

state (called AC power) and another rail supply the core logic, input buffers and output buffers in steady-state (called DC rail). A

third rail provides 5V bias voltage to 5V tolerant IO.

The rails are not connected internally. This precaution reduces the effects of simultaneous switching outputs and undesirable RF

radiation fromthe chip.

T_O

T_I/O

G

3V3

5V

5V tolerant output

5V tolerant bi-directional

Ground

3.3V power

5V bias power

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OXFW911 | IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW911-TQ-A | IEEE1394 to ATA/ATAPI Native Bridge |

| OZ6812 | ACPI CardBus Controller |

| OZ6812B | ACPI CardBus Controller |

| OZ6812T | ACPI CardBus Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OXFW911 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW911PLUS | 制造商:OXFORD 制造商全稱:OXFORD 功能描述:1394A-to-ATA7/ATAPI Bridge |

| OXFW911-TQ-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IEEE1394 to ATA/ATAPI Native Bridge |

| OXFW912 | 制造商:OXFORD 制造商全稱:OXFORD 功能描述:1394B-to-ATA7/ATAPI Bridge |

| OXFW970-TQAG | 功能描述:USB 接口集成電路 2 in 8 out FireWire audio Cont. RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。