- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224604 > NT5TU64M16DG-3C (NANYA TECHNOLOGY CORP) 64M X 16 DDR DRAM, 0.45 ns, PBGA84 PDF資料下載

參數(shù)資料

| 型號(hào): | NT5TU64M16DG-3C |

| 廠商: | NANYA TECHNOLOGY CORP |

| 元件分類: | DRAM |

| 英文描述: | 64M X 16 DDR DRAM, 0.45 ns, PBGA84 |

| 封裝: | GREEN, BGA-84 |

| 文件頁數(shù): | 22/85頁 |

| 文件大小: | 2622K |

| 代理商: | NT5TU64M16DG-3C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁

NT5TU256M4GE / NT5TU128M8GE / NT5TU64M16GG

1Gb DDR2 SDRAM

29

REV 1.0

06 / 2010

Burst Mode Operation

Burst mode operation is used to provide a constant flow of data to memory locations (write cycle), or from

memory locations (read cycle). The parameters that define how the burst mode will operate are burst sequence

and burst length. The DDR2 SDRAM supports 4 bit and 8 bit burst modes only. For 8 bit burst mode, full

interleave address ordering is supported, however, sequential address ordering is nibble based for ease of

implementation. The burst type, either sequential or interleaved, is programmable and defined by the address

bit 3 (A3) of the MRS. Seamless burst read or write operations are supported. Interruption of a burst read or

write operation is prohibited, when burst length = 4 is programmed. For burst interruption of a read or write

burst when burst length = 8 is used, see the

“Burst Interruption “section of this datasheet. A Burst Stop

command is not supported on DDR2 SDRAM devices.

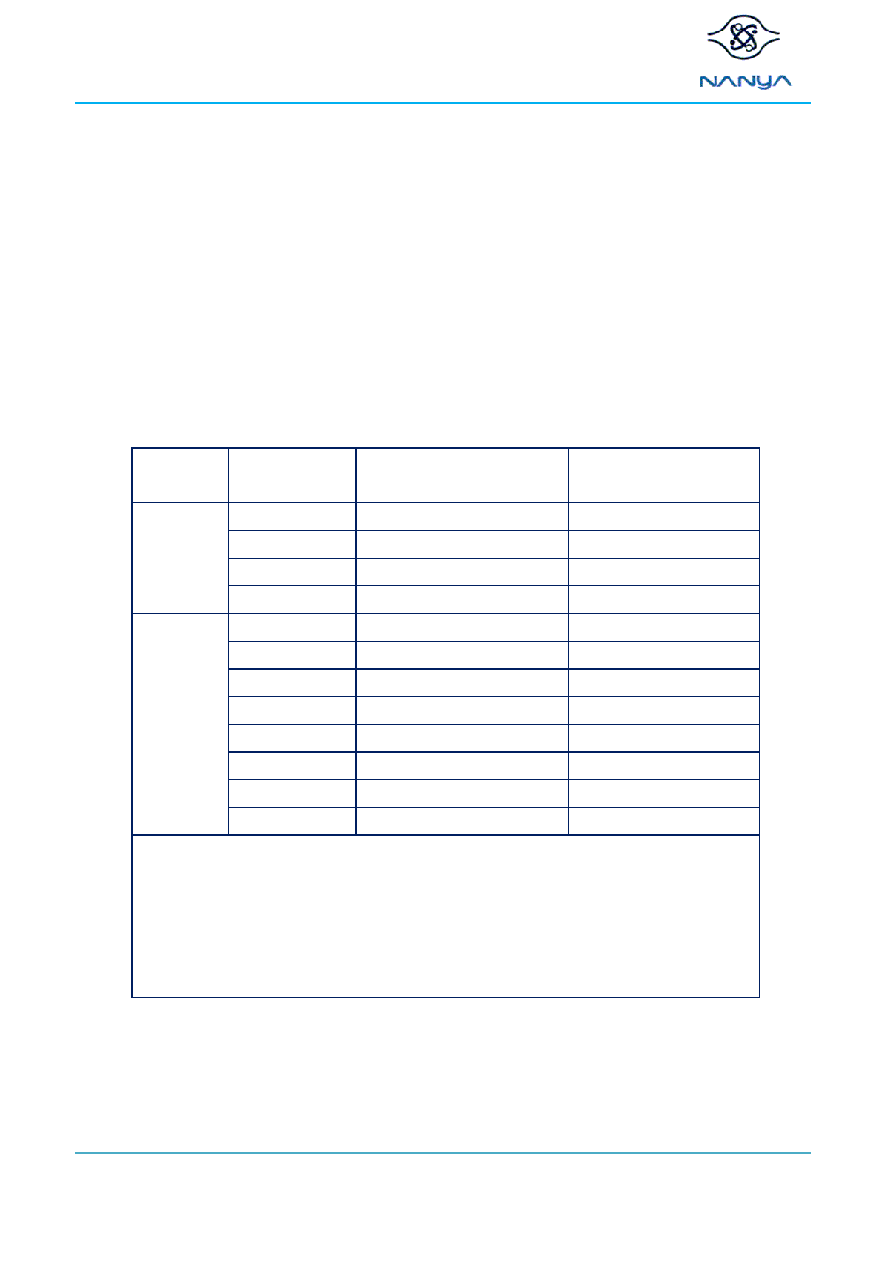

Bust Length and Sequence

Burst Length

Starting Address

(A2 A1 A0)

Sequential Addressing

(decimal)

Interleave Addressing

(decimal)

4

x

0

0,

1,

2,

3

0,

1,

2,

3

x

0

1

1,

2,

3,

0

1,

0,

3,

2

x

1

0

2,

3,

0,

1

2,

3,

0,

1

x

1

3,

0,

1,

2

3,

2,

1,

0

8

0

0,

1,

2,

3,

4,

5,

6,

7

0,

1,

2,

3,

4,

5,

6,

7

0

1

1,

2,

3,

0,

5,

6,

7,

4

1,

0,

3,

2,

5,

4,

7,

6

0

1

0

2,

3,

0,

1,

6,

7,

4,

5

2,

3,

0,

1,

6,

7,

4,

5

0

1

3,

0,

1,

2,

7,

4,

5,

6

3,

2,

1,

0,

7,

6,

5,

4

1

0

4,

5,

6,

7,

0,

1,

2,

3

4,

5,

6,

7,

0,

1,

2,

3

1

0

1

5,

6,

7,

4,

1,

2,

3,

0

5,

4,

7,

6,

1,

0,

3,

2

1

0

6,

7,

4,

5,

2,

3,

0,

1

6,

7,

4,

5,

2,

3,

0,

1

7,

4,

5,

6,

3,

0,

1,

2

7,

6,

5,

4,

3,

2,

1,

0

Note:

1) Page length is a function of I/O organization

64Mb X 16 organization (CA0-CA9); Page Size = 2K Byte; Page Length = 1024

128Mb X 8 organization (CA0-CA9 ); Page Size = 1K Byte; Page Length = 1024

256Mb x 4 organization (CA0-CA9, CA11); Page Size = 1K Byte; Page Length = 2048

2) Order of burst access for sequential addressing is "nibble-based" and therefore

different from SDR or

DDR components

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NTA2425E | |

| NTA2425F | |

| NTA2410-10 | |

| NTD2410F | |

| NTA2425-10 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NT5TU64M16GG-AC | 制造商:Nanya Technology Corporation 功能描述:DRAM |

| NT5TU64M16GG-ACI | 制造商:Nanya Technology Corporation 功能描述:DRAM |

| NT5TU64M16HG-AC | 制造商:Nanya Technology Corporation 功能描述:MEMORY IC |

| NT5TU64M16HG-BE | 制造商:Nanya Technology Corporation 功能描述:MEMORY IC |

| NT6 | 功能描述:烙鐵 Weller Chisel Tip For WMP Solder Penc RoHS:否 制造商:Weller 產(chǎn)品:Soldering Stations 類型:Digital, Iron, Stand, Cleaner 瓦特:50 W 最大溫度:+ 850 F 電纜類型:US Cord Included |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。