- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359677 > MT9173AP1 (ZARLINK SEMICONDUCTOR INC) Digital Subscriber Interface Circuit with RxSB Digital Network Interface Circuit with RxSB PDF資料下載

參數(shù)資料

| 型號: | MT9173AP1 |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | Digital Subscriber Interface Circuit with RxSB Digital Network Interface Circuit with RxSB |

| 中文描述: | DATACOM, DIGITAL SLIC, PQCC28 |

| 封裝: | LEAD FREE, PLASTIC, MS-018AB, LCC-28 |

| 文件頁數(shù): | 12/28頁 |

| 文件大小: | 613K |

| 代理商: | MT9173AP1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

MT9173/74

Data Sheet

12

Zarlink Semiconductor Inc.

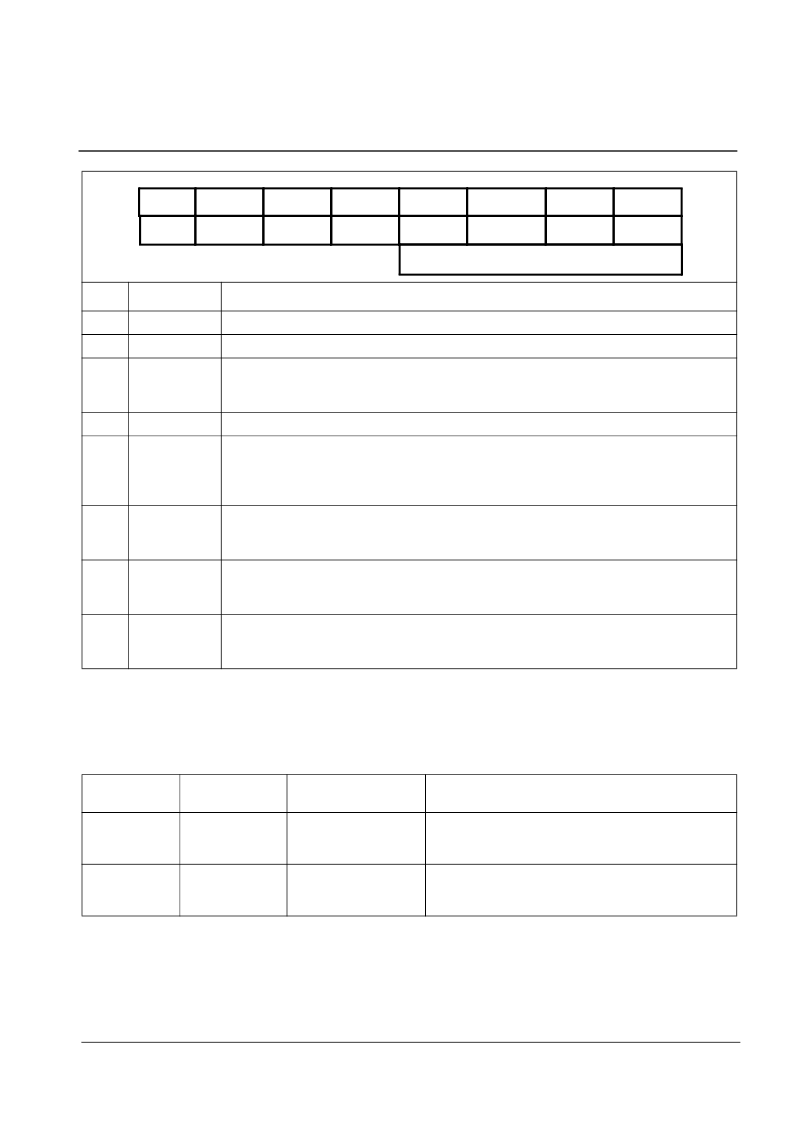

Table 4 - Control Register

Note 1:

Suggested use of ATTACK:

-

At 160 kbit/s full convergence requires 850 ms with ATTACK held high for the first 240 frames or 30 ms.

-At 80 kbit/s full convergence requires 1.75 s with ATTACK held high for the first 480 frames or 60 ms.

Note 2:

When bits 4-7 of the Control Register are all set to one, the DNIC operates in one of the default modes as defined in Table 4a,

depending upon the status of bit-3.

Table 4a. Default Mode Selection

Note 3:

Default Mode 1 can also be selected by tying CDSTi/CDi pin low when DNIC is operating in dual mode.

Note 4:

Default Mode 2 can also be selected by tying CDSTi/CDi pin high when DNIC is operating in dual mode.

Bit

Name

Description

0

Reg Sel-1

Register Select-1. Must be set to’0’ to select the Control Register.

1

Reg Sel-2

Register Select-2. Must be set to’0’ to select the Control Register.

2

DRR

Diagnostics Register Reset. Writing a "0" to this bit will cause a diagnostics register reset

to occur coincident with the next frame pulse as in the MT8972A. When this bit is a logic

"1", the Diagnostics Register will not be reset.

3

BRS

DINB

2

Bit Rate Select. When set to ’0’ selects 80 kbit/s. When set to ’1’, selects 160 kbit/s.

4

D-Channel in B Timeslot. When ’0’, the D-channel bits (D0 or D0 and D1) corresponding

to the selected bit rate (80 or 160 kbit/s) are transmitted during the normal D-channel bit

times. When set to ’1’, the entire D-channel (D0-D7) is transmitted during the B1-channel

timeslot on the line providing a 64 kbit/s D-channel link.

5

PSEN

2

Prescrambler/Deprescrambler Enable. When set to ’1’, the data prescrambler and

deprescrambler are enabled. When set to ’0’, the data prescrambler and deprescrambler

are disabled.

6

ATTACK

2

Convergence Speedup. When set to ’1’, the echo canceller will converge to the reflection

coefficient much faster. Used on power-up for fast convergence.

1

When ’0’, the echo

canceller will require the normal amount of time to converge to a reflection coefficient.

7

TxHK

2

Transmit Housekeeping. When set to ’0’, logic zero is transmitted over the line as

Housekeeping Bit. When set to ’1’, logic one is transmitted over the line as

Housekeeping Bit.

C-Channel

(Bit 0-7)

Internal Control

Register

Internal Diagnostic

Register

Description

XXX01111

00000000

01000000

Default Mode-1

3

: Bit rate is 80 kbit/s. ATTACK,

PSEN, DINB, DRR and all diagnostics are disabled.

TxHK=0.

Default Mode-2

4

Bit rate is 160 kbit/s. ATTACK,

PSEN, DINB, DRR and all diagnostics are disabled.

TxHK=0.

XXX11111

00010000

01000000

bit 0

bit 1

bit 2

bit 3

bit 4

bit 5

bit 6

bit 7

Reg Sel-1

Reg Sel-2

DRR

BRS

DINB

PSEN

ATTACK

TxHK

Default Mode Selection (Refer to Table 4a)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT3370B | Wide Dynamic Range DTMF Receiver |

| MT3370BN | Wide Dynamic Range DTMF Receiver |

| MT3370BS | Wide Dynamic Range DTMF Receiver |

| MT3370BSR | Wide Dynamic Range DTMF Receiver |

| MT3370BSR1 | Wide Dynamic Range DTMF Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9174 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS ST-BUS⑩ FAMILY Digital Network Interface Circuit with Receive Sync Marker Bit |

| MT9174AE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Digital Subscriber Interface Circuit with RxSB Digital Network Interface Circuit with RxSB |

| MT9174AN | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 24SSOP - Rail/Tube |

| MT9174AN1 | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 24SSOP - Rail/Tube 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SUBSCRIBER NETWRK DNIC 24SSOP 制造商:Microsemi Corporation 功能描述:IC SUBSCRIBER NETWRK DNIC 24SSOP |

| MT9174AP | 制造商:Microsemi Corporation 功能描述:DGTL INTRFC CIRCUIT 24PLCC - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。