- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383642 > MT8930CC (Mitel Networks Corporation) CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information PDF資料下載

參數(shù)資料

| 型號: | MT8930CC |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit Preliminary Information |

| 中文描述: | 意法半導(dǎo)體的CMOS總線⑩家庭用戶網(wǎng)絡(luò)接口電路的初步信息 |

| 文件頁數(shù): | 20/42頁 |

| 文件大?。?/td> | 323K |

| 代理商: | MT8930CC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

MT8930C

9-52

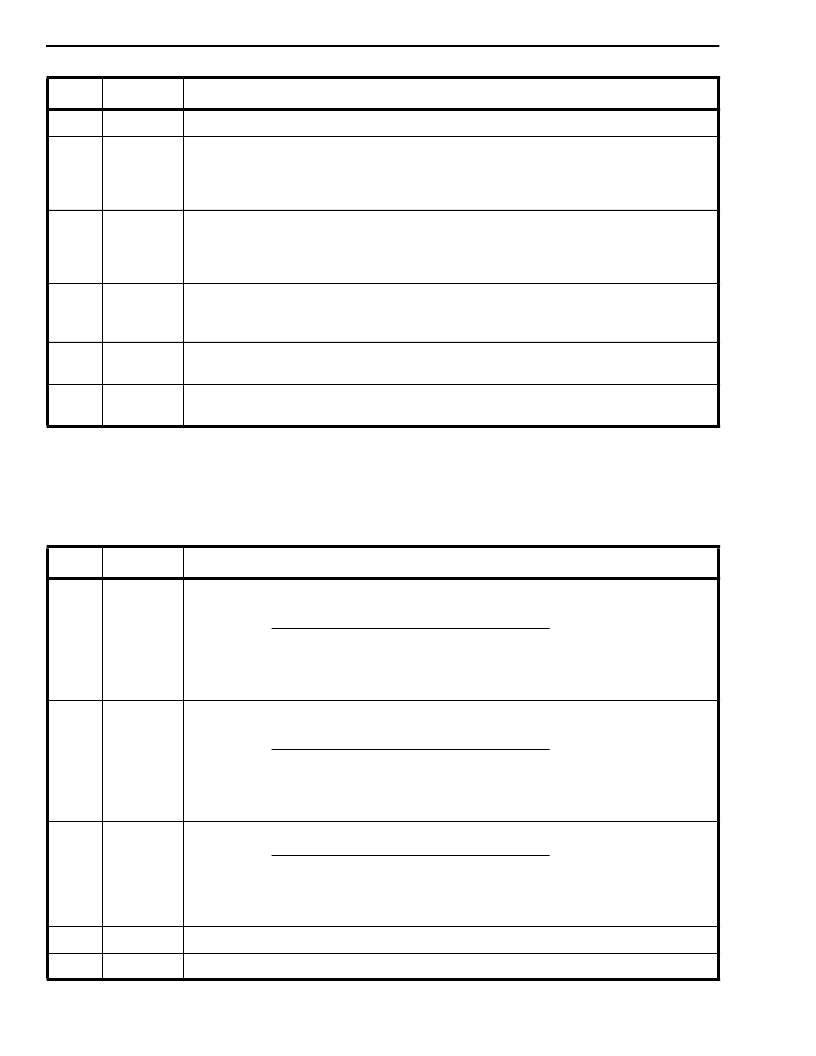

Table 7. HDLC Control Register 2 (Write Add. 00011

B

)

Note 2: These bits will be reset after a write to the TxFIFO

Table 8. HDLC Status Register (Read Add. 00011

B

)

BIT

NAME

DESCRIPTION

B7-B5

NA

Keep at ’0’ for normal operation.

B4

Trans

A ’1’ will place the HDLC in a transparent mode. This will perform the serial to parallel or

parallel to serial conversion without inserting or deleting the opening and closing flags,

CRC bytes or zero insertion. The source or destination of the data is determined by the

port selection bits in the HDLC Control Register 1.

B3

RxRst

A transition from ‘0’ to ’1’ will reset the receive FIFO. This causes the receiver to be

disabled until the reception of the next flag. (The status Register will identify the RxFIFO

as being empty). The device resets this bit to ‘0’ immediately after clearing the receive

FIFO.

B2

TxRst

A transition from ‘0’ to ’1’ will reset the transmit FIFO. This causes the transmitter to

clear all data in the TxFIFO. The device resets this bit to ‘0’ immediately after clearing

the transmit FIFO.

B1

FA

(2)

A ’1’ will ’tag’ the next byte written to the transmit FIFO and cause an abort sequence to

be transmitted once it reaches the bottom of the FIFO.

B0

EOP

(2)

A ’1’ will ’tag’ the next byte written to the transmit FIFO and cause an end of packet

sequence to be transmitted once it reaches the bottom of the FIFO.

BIT

NAME

DESCRIPTION

B7-B6

RxByte

Status

These two bits indicate the status of the received byte which is ready to be read from the

19 deep received FIFO. The status is encoded as follows:

B7 -B6

0 - 0

- Packet Byte

0 - 1

- First Byte

1 - 0

- Last Byte (Good FCS)

1 - 1

- Last Byte (Bad FCS)

B5-B4

RxFIFO

Status

These two bits indicate the status of the 19 deep receive FIFO. This status is encoded

as follows:

B5 - B4

0 - 0

- Rx FIFO Empty

0 - 0

-

≤

14 Bytes

1 - 0

- Rx FIFO Overflow

1 - 1

-

≥

15 Bytes

B3-B2

TxFIFO

Status

These two bits indicate the status of the 19 deep transmit FIFO as follows:

B3 - B2

0 - 0

- Tx FIFO Full

0 - 1

-

≥

5 Bytes

1 - 0

- Tx FIFO Empty

1 - 1

-

≤

Bytes

B1

Idle

If ’1’, an idle channel state has been detected.

B0

Int

If ’1’ an unmasked asynchronous interrupt has been detected.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT8930CE | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8930CP | CMOS ST-BUS⑩ FAMILY Subscriber Network Interface Circuit |

| MT8931C | Subscriber Network Interface Circuit(用戶網(wǎng)絡(luò)接口電路(提供點到點或點到多點數(shù)字傳送)) |

| MT8940 | T1/CEPT Digital Trunk PLL(T1/CEPT數(shù)字中繼鎖相環(huán)) |

| MT8940 | ISO-CMOS ST-BUS⑩ FAMILY T1/CEPT Digital Trunk PLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8930CE | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:Subscriber Network Interface Circuit |

| MT8930CPR | 制造商:Microsemi Corporation 功能描述: |

| MT8931B | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

| MT8931BC | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Subscriber Network Interface Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。