- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384759 > MT8920BC (Mitel Networks Corporation) ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit PDF資料下載

參數(shù)資料

| 型號: | MT8920BC |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| 中文描述: | 異意法半導體的CMOS總線⑩家庭圣總線并行訪問電路 |

| 文件頁數(shù): | 2/24頁 |

| 文件大小: | 534K |

| 代理商: | MT8920BC |

MT8920B

CMOS

3-4

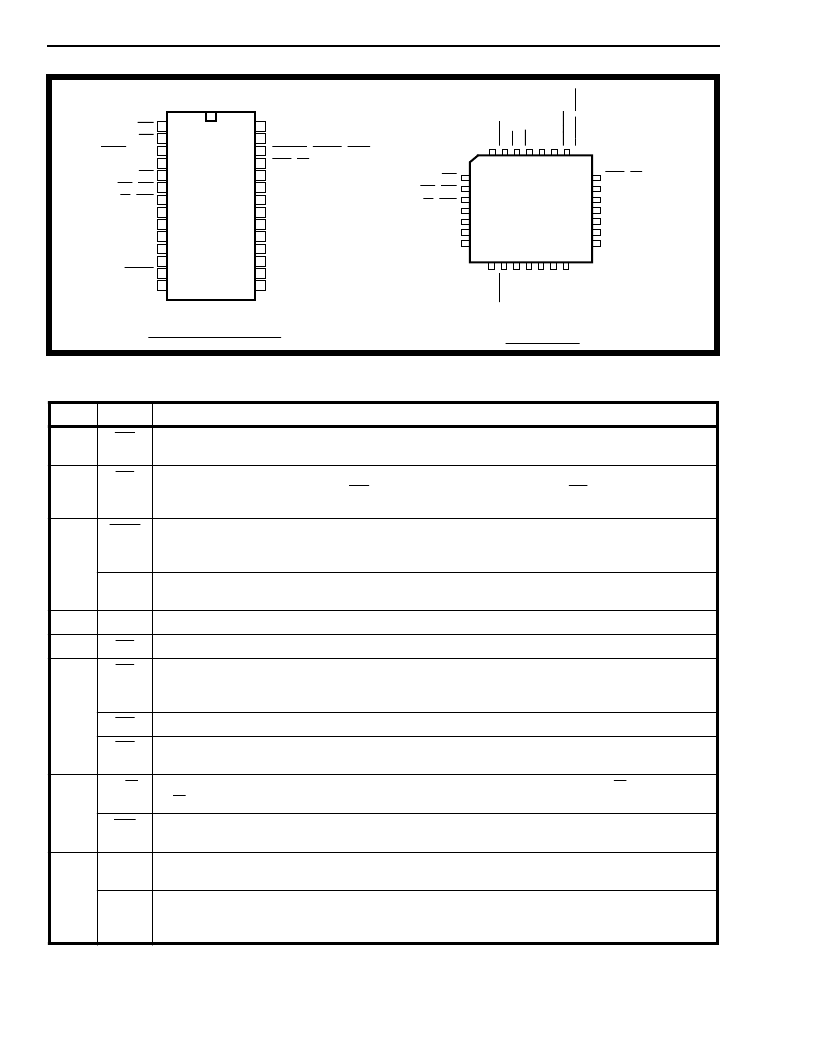

Figure 2 - Pin Connections

Pin Description

Pin #

Name

Description

1

C4i

4.096 MHz Clock.

The ST-BUS timing clock used to establish bit cell boundaries for the serial

bus.

2

F0i

Framing Pulse.

A low going pulse used to synchronize the STPA to the 2048 kbit/s ST-BUS

stream. The first falling edge of C4i subsequent to the falling edge of F0i identifies the start of

a frame.

3

IACK

Interrupt Acknowledge (Mode 1).

This active low input signals that the current bus cycle is

an interrupt vector fetch cycle. Upon receiving this acknowledgement, the STPA will

output a user-programmed vector number on D

0

- D

7

indicating the source of the interrupt.

Mode Select 1 (Mode 2,3).

This input is used to select the device operating modes. A low

applied to this pin will select mode 3 while a high will select mode 2. (Refer to Table 1.)

MS1

4

STi0

ST-BUS Input 0.

This is the input for the 2048 kbit/s ST-BUS serial data stream.

5

CS

Chip Select.

This active low input is used to select the STPA for a parallel access .

6

DS

Data Strobe (Mode 1).

This active low input indicates to the STPA that valid data is on the data

bus during a write operation or that the STPA must output valid data on the data bus during a

read operation.

OE

Output Enable (Mode 2).

This active low input enables the data bus driver outputs.

OE

Output Enable (Mode 3).

This active low output indicates that the selected device is to be

read and that the data bus is available for data transfer.

7

R/W

Read/Write (Mode 1,2).

This input defines the data bus transfer as a read (R/W = 1) or a write

(R/W= 0) cycle.

WE

Write Enable (Mode 3).

This active low output indicates the data on the data bus is to be

written into the selected location of an external device.

8-12

A0-A4

Address Bus (Mode 1,2).

These inputs are used to select the internal registers and two-port

memories of the STPA.

A0-A4

Address Bus (Mode 3).

These address outputs are generated by the STPA and reflect the

position in internal RAM where the information will be fetched from or stored in. Addresses

generated in this mode are used to access external devices for direct memory transfer.

28 PIN J-LEAD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

28

27

26

25

24

23

22

21

C4i

F0i

IACK, MS1

STi0

CS

DS, OE

R/W, WE

A0

A1

A2

A3

A4

A5, STCH

VSS

VDD

MMS

DTACK, BUSY, DCS

IRQ, 24/32

STo1

STo0

D7

D6

D5

D4

D3

D2

D1

D0

28 PIN PDIP/CERDIP/SOIC

2

4

3

2

1

2

2

5

6

7

8

9

10

11

25

24

23

22

21

20

19

1

1

1

1

1

1

1

F

I

S

C

V

M

D

IRQ, 24/32

STo1

STo0

D7

D6

D5

D4

CS

DS, OE

R/W, WE

A0

A1

A2

A3

A

V

D

D

D

D

B

A

相關PDF資料 |

PDF描述 |

|---|---|

| MT8920BE | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8920BP | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8920BS | ISO-CMOS ST-BUS⑩ FAMILY ST-BUS Parallel Access Circuit |

| MT8926 | ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) |

| MT8926AE | ISO-CMOS ST-BUS⑩ FAMILY T1 Performance Monitoring Adjunct Circuit (PMAC) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT8920BE | 制造商:Mitel Networks Corporation 功能描述:COMMUNICATIONS INTERFACE, 28 Pin, Plastic, DIP |

| MT8920BE1 | 制造商:Zarlink Semiconductor Inc 功能描述:ST-BUS PARALLEL ACCESS CIRCUIT 28PDIP - Rail/Tube 制造商:Microsemi 功能描述:Microsemi MT8920BE1 Interface Misc |

| MT8920BP | 制造商:Microsemi Corporation 功能描述: 制造商:MITEL 功能描述: |

| MT8920BP1 | 制造商:Microsemi Corporation 功能描述:ST-BUS PARALLEL ACCESS CIRCUIT 28PLCC - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:ST-BUS PARALLEL ACCESS CIRCUIT 28PLCC - Rail/Tube |

| MT8920BPR1 | 制造商:Microsemi Corporation 功能描述:ST-BUS PARALLEL ACCESS CIRCUIT 28PLCC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:ST-BUS PARALLEL ACCESS CIRCUIT 28PLCC - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。