- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384759 > MT4LDT464HS (Micron Technology, Inc.) SMALL-OUTLINE DRAM MODULE PDF資料下載

參數(shù)資料

| 型號: | MT4LDT464HS |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | SMALL-OUTLINE DRAM MODULE |

| 中文描述: | 小外形DRAM模塊 |

| 文件頁數(shù): | 2/32頁 |

| 文件大?。?/td> | 625K |

| 代理商: | MT4LDT464HS |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

4, 8 Meg x 64 DRAM SODIMMs

DM83.p65 – Rev. 2/99

Micron Technology, Inc., reserves the right to change products or specifications without notice.

1999, Micron Technology, Inc.

2

4, 8 MEG x 64

DRAM SODIMMs

CAS#. Additional columns may be accessed by provid-

ing valid column addresses, strobing CAS# and hold-

ing RAS# LOW, thus executing faster memory cycles.

Returning RAS# HIGH terminates the FAST-PAGE-

MODE operation.

EDO PAGE MODE

EDO PAGE MODE, designated by the “X” option,

is an accelerated FAST-PAGE-MODE cycle. The pri-

mary advantage of EDO is the availability of data-out

even after CAS# goes back HIGH. EDO provides for

CAS# precharge time (

t

CP) to occur without the out-

put data going invalid. This elimination of CAS#

output control provides for pipelined READs.

FAST-PAGE-MODE modules have traditionally

turned the output buffers off (High-Z) with the rising

edge of CAS#. EDO operates as any DRAM READ or

FAST-PAGE-MODE READ, except data will be held

valid after CAS# goes HIGH, as long as RAS# and OE#

are held LOW and WE# is held HIGH. (Refer to the 8

Meg x 8 EDO DRAM data sheet for additional infor-

mation on EDO functionality.)

REFRESH

Memory cell data is retained in its correct state by

maintaining power and executing any RAS# cycle

(READ, WRITE) or RAS# refresh cycle (RAS#-ONLY,

CBR or HIDDEN) so that all combinations of RAS#

addresses are executed at least every

t

REF, regardless of

sequence. The CBR REFRESH cycle will invoke the

internal refresh counter for automatic RAS# address-

ing.

An optional self refresh mode is also available on

the “S” version. The “S” option allows the user the

choice of a fully static, low-power data retention mode

or a dynamic refresh mode at the extended refresh

period of 128ms, or 125μs per row when using distrib-

uted CBR REFESH. The optional self refresh feature is

initiated by performing a CBR REFRESH cycle and

holding RAS# LOW for the specified

t

RASS.

The self refresh mode is terminated by driving RAS#

HIGH for a minimum time of

t

RPS. This delay allows

for the completion of any internal refresh cycles that

may be in process at the time of the RAS# LOW-to-

HIGH transition. If the DRAM controller uses a distrib-

uted refresh sequence, a burst refresh is not required

upon exiting self refresh. However, if the DRAM con-

troller utilizes a RAS#-ONLY or burst refresh sequence,

all 1,240 rows must be refreshed within the average

internal refresh rate, prior to the resumption of normal

operation.

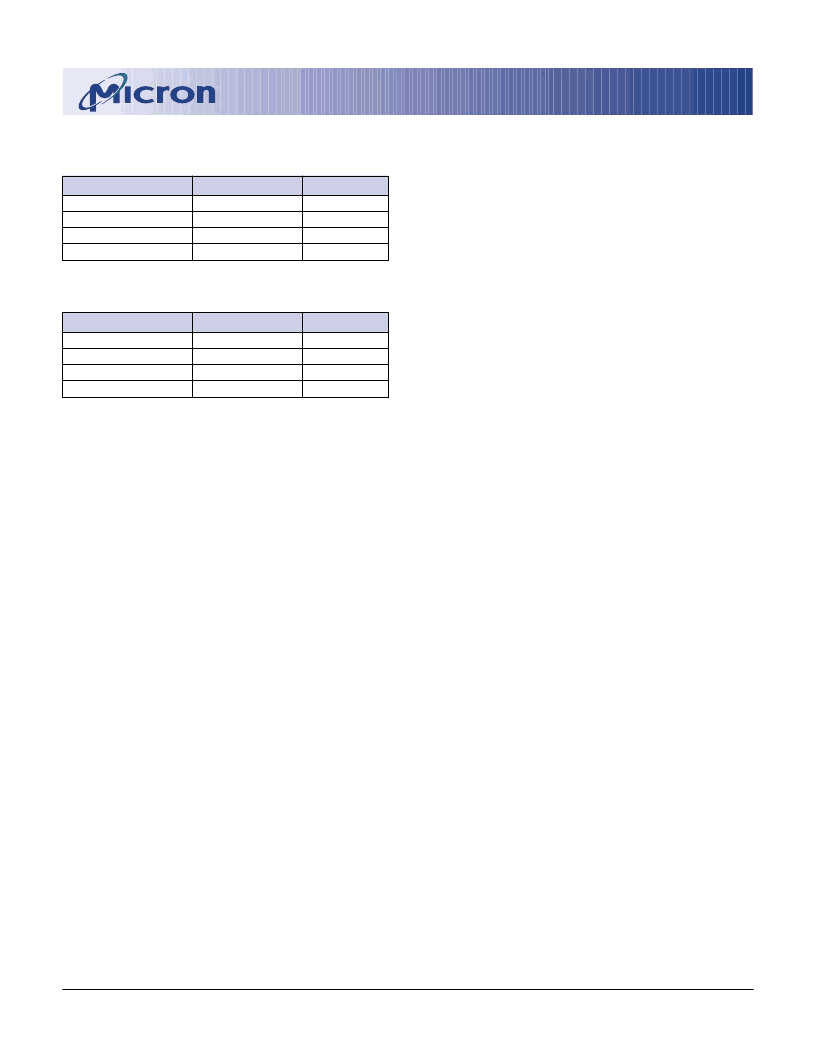

PART NUMBERS

FPM Operating Mode

PART NUMBER

MT4LDT464HG-x

MT4LDT464HG-x S

MT8LDT864HG-x

MT8LDT864HG-x S

x = speed

CONFIGURATION

4 Meg x 64

4 Meg x 64

8 Meg x 64

8 Meg x 64

REFRESH

Standard

Self

Standard

Self

EDO Operating Mode

PART NUMBER

MT4LDT464HG-x X

MT4LDT464HG-x XS

MT8LDT864HG-x X

MT8LDT864HG-x XS

x = speed

CONFIGURATION

4 Meg x 64

4 Meg x 64

8 Meg x 64

8 Meg x 64

REFRESH

Standard

Self

Standard

Self

GENERAL DESCRIPTION

The MT4LDT464H (X)(S) and MT8LDT864H (X)(S)

are randomly accessed 32MB and 64MB memories

organized in a small-outline, x64 configuration. They

are specially processed to operate from 3V to 3.6V for

low-voltage memory systems.

During READ or WRITE cycles, each location is

uniquely addressed via the address bits. The row ad-

dress is latched by the RAS# signal, then the column

address is latched by the CAS# signal.

READ and WRITE cycles are selected with the WE#

input. A logic HIGH on WE# dictates read mode, while

a logic LOW on WE# dictates write mode. During a

WRITE cycle, data-in (D) is latched by the falling edge

of WE# or CAS#, whichever occurs last. An EARLY

WRITE occurs when WE# is taken LOW prior to CAS#

falling. A LATE WRITE or READ-MODIFY-WRITE oc-

curs when WE# falls after CAS# is taken LOW. During

EARLY WRITE cycles, the data outputs (Q) will remain

High-Z, regardless of the state of OE#. During LATE

WRITE or READ-MODIFY-WRITE cycles, OE# must be

taken HIGH to disable the data outputs prior to apply-

ing input data. If a LATE WRITE or READ-MODIFY-

WRITE is attempted while keeping OE# LOW, no

WRITE will occur, and the data outputs will drive read

data from the access location.

FAST PAGE MODE

FAST-PAGE-MODE operations allow faster data

operations (READ or WRITE) within a row-address-

defined page boundary. The FAST-PAGE-MODE cycle

is always initiated with a row address strobed in by

RAS#, followed by a column address strobed in by

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT4LDT464HX | SMALL-OUTLINE DRAM MODULE |

| MT8LSDT864 | SMALL-OUTLINE SDRAM MODULE |

| MT4LSDT464H | SMALL-OUTLINE SDRAM MODULE |

| MT4LSDT464L | SMALL-OUTLINE SDRAM MODULE |

| MT4LSDT464LH | SMALL-OUTLINE SDRAM MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT4LDT464HX | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SMALL-OUTLINE DRAM MODULE |

| MT4LDT464HXS | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SMALL-OUTLINE DRAM MODULE |

| MT4LDT832HG-5X | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SMALL-OUTLINE DRAM MODULE |

| MT4LDT832HG-5XS | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SMALL-OUTLINE DRAM MODULE |

| MT4LDT832HG-6X | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:SMALL-OUTLINE DRAM MODULE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。