- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45354 > MPC8245TZU333D (MOTOROLA INC) 32-BIT, 333 MHz, RISC PROCESSOR, PBGA352 PDF資料下載

參數(shù)資料

| 型號: | MPC8245TZU333D |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 333 MHz, RISC PROCESSOR, PBGA352 |

| 封裝: | 35 X 35 MM, 1.70 MM HEIGHT, 1.27 MM PITCH, CAVITY-UP, TBGA-352 |

| 文件頁數(shù): | 32/60頁 |

| 文件大?。?/td> | 674K |

| 代理商: | MPC8245TZU333D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

38

MPC8245 Integrated Processor Hardware Specications

MOTOROLA

PLL Configuration

1.6

PLL Conguration

The internal PLLs of the MPC8245 are congured by the PLL_CFG[0:4] signals. For a given

PCI_SYNC_IN (PCI bus) frequency, the PLL conguration signals set both the peripheral logic/memory

bus PLL (VCO) frequency of operation for the PCI-to-memory frequency multiplying and the MPC603e

CPU PLL (VCO) frequency of operation for memory-to-CPU frequency multiplying. The PLL

DA[14:15]

F1 J2

Output

GVDD

2, 6

Notes:

1.

Place a pull-up resistor of 120

or less on the TEST0 pin.

2.

Treat these pins as no connects (NC) unless using debug address functionality.

3.

This pin has an internal pull-up resistor which is enabled only when the MPC8245 is in the reset state. The value

of the internal pull-up resistor is not guaranteed, but is sufcient to ensure that a logic 1 is read into conguration

bits during reset.

4.

This pin is a reset conguration pin.

5.

DL[0] is a reset conguration pin and has an internal pull-up resistor which is enabled only when the MPC8245 is

in the reset state. The value of the internal pull-up resistor is not guaranteed, but is sufcient to ensure that a logic 1

is read into conguration bits during reset.

6.

Multi-pin signals such as AD[31:0] or MDL[0:31] have their physical package pin numbers listed in order,

corresponding to the signal names. Example: AD0 is on pin C22, AD1 is on pin D22, ..., AD31 is on pin V25.

7.

GNT4 is a reset conguration pin and has an internal pull-up resistor which is enabled only when the MPC8245 is

in the reset state.

8.

Recommend a weak pull-up resistor (2–10 k

) be placed on this PCI control pin to LVDD.

9.

10. Recommend a weak pull-up resistor (2–10 k

) be placed on this pin to OVDD.

11. Recommend a weak pull-up resistor (2–10 k

) be placed on this pin to GVDD.

12. This pin has an internal pull-up resistor which is enabled at all times. The value of the internal pull-up resistor is

not guaranteed, but is sufcient to prevent unused inputs from oating.

13. External PCI clocking source or fan-out buffer may be required for system if using the MPC8245 DUART

functionality since PCI_CLK[0:3] are not available in DUART mode. Only PCI_CLK4 is available in DUART mode.

14. This pin is a multiplexed signal and appears more than once in this table.

15. This pin is affected by programmable PCI_HOLD_DEL parameter.

16. This pin is an open drain signal.

17. This pin can be programmed to be driven (default) or can be programmed (in PMCR2) to be open drain.

18. This pin is a sustained three-state pin as dened by the PCI Local Bus Specication.

19. OSC_IN utilizes the 3.3-V PCI interface driver which is 5-V tolerant, see Table 2 for details.

20. PLL_CFG[0:4] signals are sampled a few clocks after the negation of HRST_CPU and HRST_CTRL.

21. SDRAM_CLK[0:3] and SDRAM_SYNC_OUT signals use DRV_MEM_CTRL for chip Rev 1.1 (A). These signals

use DRV_MEM_CLK for chip Rev 1.2 (B).

22. The 266- and 300-MHz part offerings can be run at a source voltage of 1.8 ± 100 mV or 2.0 ± 100 mV. Note that

source voltage should be 2.0 ± 100 mV for 333- and 350-MHz parts.

23. This pin was formally LAVDD on the MPC8240. It is a no connect on the MPC8245. This should not pose a problem

when replacing an MPC8240 with an MPC8245.

24. The driver capability of this pin is hardwired to 40

and cannot be changed.

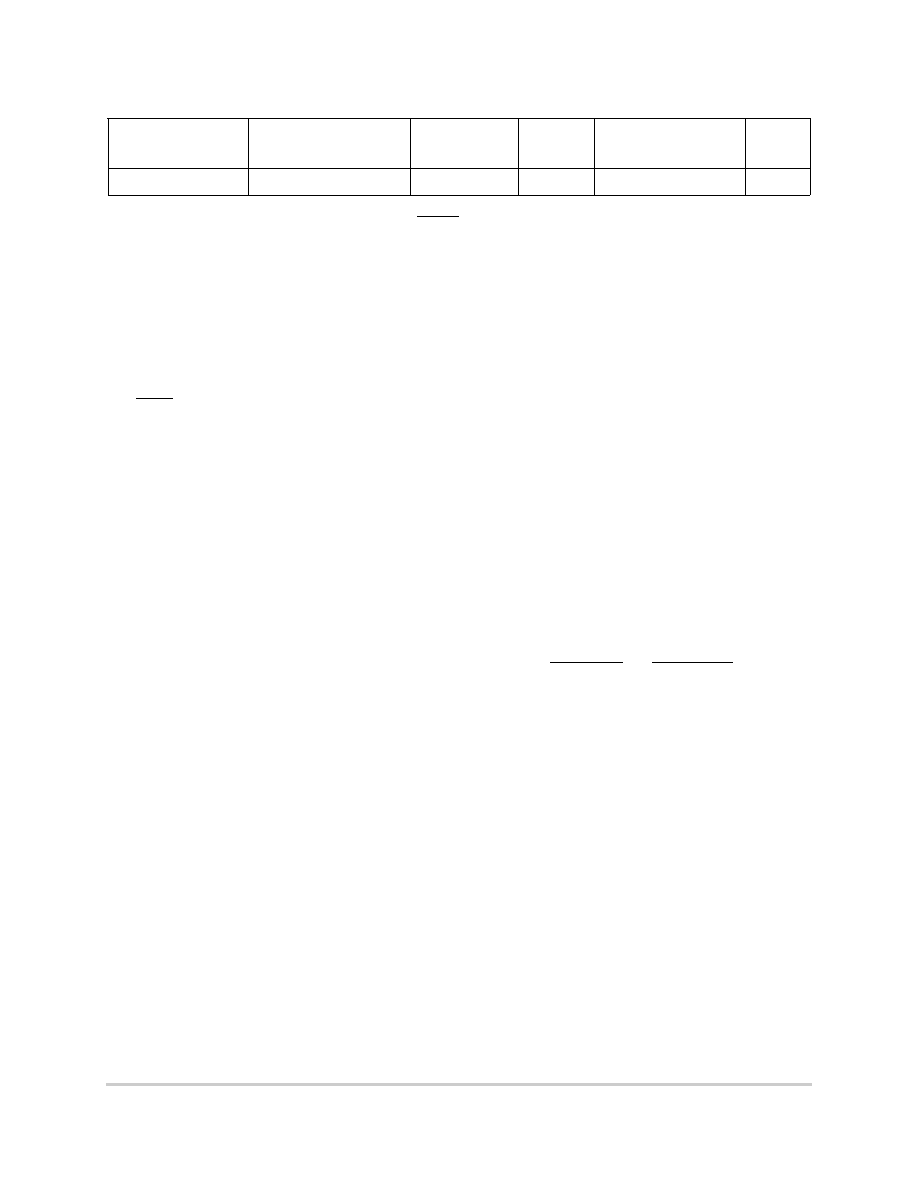

Table 17. MPC8245 Pinout Listing (continued)

Name

Pin Number

Type

Power

Supply

Output

Driver Type

Notes

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8245TVV350D | 32-BIT, 350 MHz, RISC PROCESSOR, PBGA352 |

| MPC8245TVV300D | 32-BIT, 300 MHz, RISC PROCESSOR, PBGA352 |

| MPC8250ACZQIHBX | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA516 |

| MPC8250AVVLHDX | 32-BIT, 250 MHz, RISC PROCESSOR, PBGA480 |

| MPC8250AVRIHBX | 32-BIT, 200 MHz, RISC PROCESSOR, PBGA516 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8245TZU350D | 功能描述:微處理器 - MPU 350MHz 665MIPS RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| MPC8247 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8247CVR | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MPC8272 PowerQUICC II Family Hardware Specifications |

| MPC8247CVRB | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

| MPC8247CVRE | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC II⑩ Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。