- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄102744 > ML9041A-01BCVWA (OKI ELECTRIC INDUSTRY CO LTD) 17 X 100 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC175 PDF資料下載

參數(shù)資料

| 型號(hào): | ML9041A-01BCVWA |

| 廠商: | OKI ELECTRIC INDUSTRY CO LTD |

| 元件分類(lèi): | 顯示控制器 |

| 英文描述: | 17 X 100 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC175 |

| 封裝: | 10.62 X 2.55 MM, GOLD BUMP, DIE-175 |

| 文件頁(yè)數(shù): | 14/64頁(yè) |

| 文件大小: | 653K |

| 代理商: | ML9041A-01BCVWA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)

PEDL9041A-02

OKI Semiconductor

ML9041A-xxA/xxB

21/64

Arbitrator RAM (ABRAM)

The arbitrator RAM (ABRAM) stores arbitrator display data.

100 dots can be displayed in both 1-line and 2-line display modes. The arbitrator RAM has the addresses

(hexadecimal) from “00” to “1F” and the valid display address area is from 00 to 19 (0H to 13H). The area of 20 to

31 (14H to 1FH) not used for display can be used as a data RAM area for general data. Even if the display is shifted

by instruction, the arbitrator display is not shifted.

A capacity of 8 bits by 32 addresses (= 256 bits) is available for data write.

First set the mode to increment or decrement from the CPU, and then input the ABRAM address.

Write Display-ON data in the ABRAM through DB

0 to DB7.

DB

0 to DB7 correspond to the ABRAM data bit weights 0 to 7 respectively. Input data “1” represents the ON status

of an LCD dot and “0” represents the OFF status.

Since ADC is automatically incremented or decremented by 1 after the data is written to the ABRAM, it is not

necessary to set the ABRAM address again.

Whereas ABRAM data bit weights 0 to 4 are output as display data to the LCD, the ABRAM data bit weights 5 to

7 are not. These bits can be used as a RAM area.

The cursor or blink is also displayed even when a CGRAM or ABRAM address is set in the ADC. Therefore, the

cursor or blink display should be inhibited while the ADC is holding a CGRAM or ABRAM address.

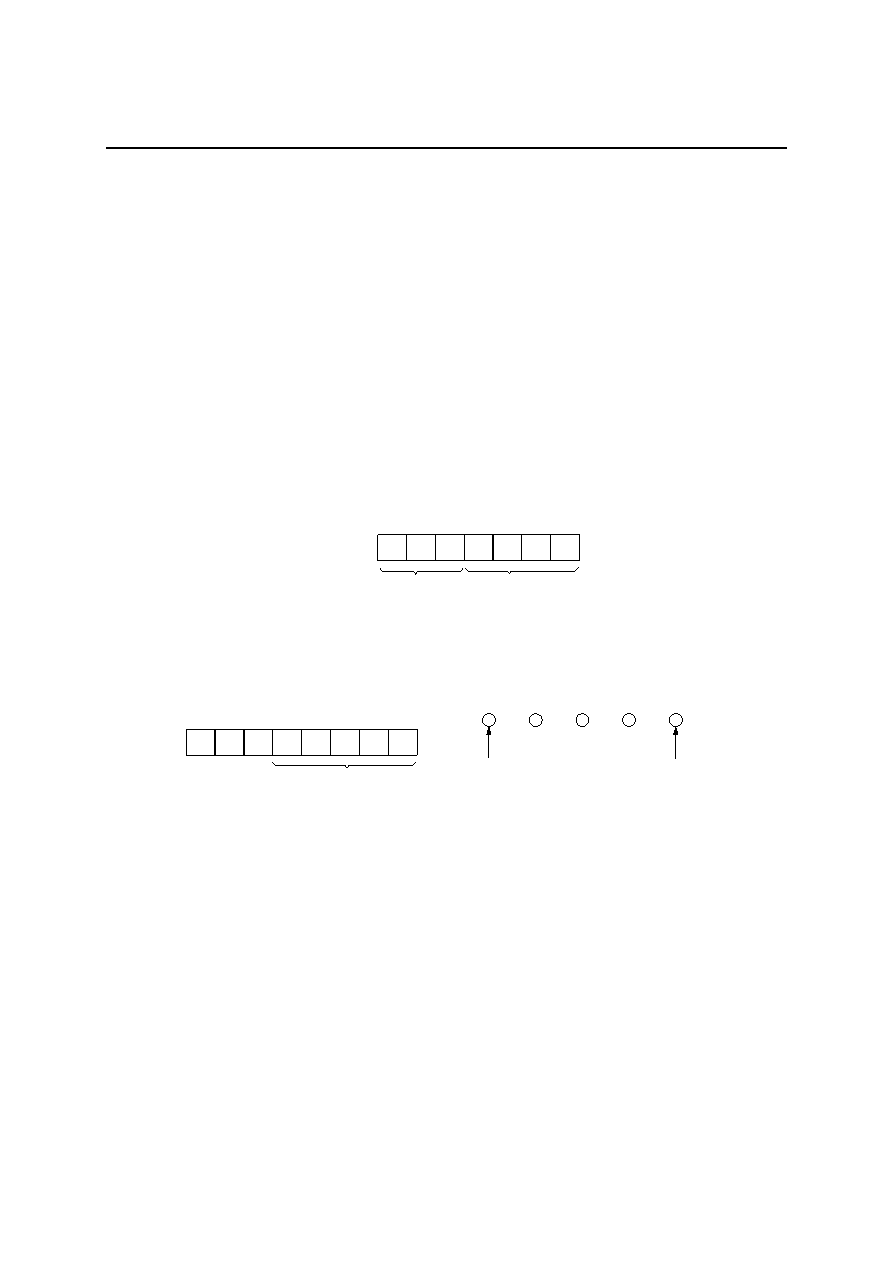

MSB

LSB

DB

6 DB5 DB4 DB3 DB2 DB1 DB0

Hexadecimal

ADC

The arbitrator RAM can store a maximum of 100 dots of the arbitrator Display-ON data in units of 5 dots.

The relationship with the LCD display positions is shown below.

*

E4 E3 E2 E1

E0

DB6

*

DB7

DB5 DB4 DB3 DB2 DB1 DB0

* Don’t Care

Display - ON data

E4

E0

5XSn+1

5XSn+5

Configuration of input display data

Input data

Relationship between display-ON

data and segment pins

Sn = ABRAM address (0 to 19)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MX10C8051FI | 8-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP44 |

| MPC8260ACZULHDX | 32-BIT, 250 MHz, RISC PROCESSOR, PBGA480 |

| MPC8266ACZUMIBX | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA480 |

| M38267E8GP | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP100 |

| M37281EKSP | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP52 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ML9041A-XXACVWA | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:DOT MATRIX LCD CONTROLLER DRIVER |

| ML9041A-XXBCVWA | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:DOT MATRIX LCD CONTROLLER DRIVER |

| ML9042 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:DOT MATRIX LCD CONTROLLER DRIVER |

| ML9042-54CVWA-5016 | 制造商:ROHM Semiconductor 功能描述:RHOML9042-54CVWA-5016 OKI LCD DRIVER |

| ML9044 | 制造商:OKI 制造商全稱:OKI electronic componets 功能描述:DOT MATRIX LCD CONTROLLER DRIVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。